Частота pci express шины: Nothing found for Osnovy Ustrojstva Pk Shiny Pci I Pci Express %23_Pci

Содержание

Особенности шины PCI Express 3.0.

Первые продукты с поддержкой PCI Express 3.0 появились еще

в 2010 году. Реальная скорость передачи данных по PCI Express 3.0 вдвое выше,

чем у PCI Express 2.0. Материнские платы с поддержкой PCI Express 3.0 могут

работать с видеокартами, потребляющими до

300 Вт.

В версии PCI Express 3.0, максимальная полоса пропускания канала увеличена до 8

ГТ/с с незначительными изменениями

протокола обмена, форм-фактора и методов обеспечения целостности данных. В

дальнейшем предполагается увеличение скорости передачи данных за счет развития

новых технологий.

При выборе скорости передачи

данных по шине было решено остановиться на отметке 8 ГТ/с (гигатрансфер в

секунду – единица измерения, определяющая количество произведенных операций по

пересылке данных в секунду), в то время как для версии 2.0 стандарта данный

показатель был установлен на уровне 5 ГТ/с. Почти двукратного роста пропускной

Почти двукратного роста пропускной

способности удалось достичь благодаря изменениям в системе кодирования. Вместо

традиционной системы кодирования теперь будет использована технология

перестановки элементов изображения с фиксированной длиной пакетов в начале и в

конце потоков данных.

Именно для обеспечения высокой

пропускной способности при ограниченной частоте было принято решение перейти на

использование более агрессивной схемы кодирования 128b130b, которая

предусматривает передачу всего 1,6% избыточной информации, по сравнению с 20% в

текущей схеме кодирования 8b10b. Выбор такого

принципа устранения избыточности вместо перехода на 10 ГТ/с был обусловлен тем,

что 8 ГТ/с является наиболее оптимальным компромиссом между затратами,

возможностями производства, энергопотреблением и совместимостью.

К этому решению PCI SIG шла рассматривая

различные варианты из диапазона 8-10 ГТ/с. Одним из факторов, который повлиял

на окончательное решение, стала несовместимость самого быстрого варианта с

пропускной способностью 10 ГТ/с и самой первой версии стандарта с пропускной

способностью 2,5 ГТ/с. Более того, потребляемая мощность при переходе с 8 ГТ/с

Более того, потребляемая мощность при переходе с 8 ГТ/с

к 10 ГТ/с растет экспоненциально, а не линейно, как ранее. Отказаться от

повышения частоты до 10 ГГц пришлось, прежде всего, из соображений сохранения

уровня энергопотребления в разумных границах, поскольку рост частоты

сопровождается экспоненциальным увеличением потребляемой мощности.

По мнению специалистов, рост

частоты до 8 ГГц повлечет за собой значительное усложнение структуры чипов, для

реализации которых, скорее всего, понадобится применять, по меньшей мере, 65-нм

техпроцесс. Среди остальных новшеств нового стандарта отметим

усовершенствования каналов, улучшенную систему передачи сигналов, уравнивание

приема и передачи, улучшения системы фазовой автоподстройки частоты.

В составе готовых систем новые

интерфейсы начали появляться еще в 2011 г., с основным прицелом на «жадные» к

пропускной способности графические чипы в настольных системах высокого уровня и

серверы, использующие мультипортовые карты 10 Гбит Ethernet и 8 Гбит Fibre

Channel.

Что

касается устройств, для которых потребуется быстродействие PCI Express 3.0, то это

коммутаторы PLX, контроллеры Ethernet 40 Гбит/с, InfiniBand, твёрдотельные

устройства, которые становятся всё популярнее, и, конечно, видеокарты. Все

возможные инновации разработчики PCI Express еще не исчерпали, и они появляются

не статически, а непрерывным потоком, который открывает путь для дальнейших

улучшений в будущих версиях интерфейса PCI Express.

Решения

для десктопов потребительского класса

Intel P67, H67 и H61 уже не получили поддержки шины PCI, но большинство и более

современных материнских плат обладают слотами PCI. В них используются

специальные чипы-мосты PCI Express – PCI,

их поставщиком уже является, например, компания IDT (рис. 1).

|

|

|

Рис.

|

Мост

PCI Express – PCI (IDT PEB383)

поддерживает 32-битную шину PCI с тактовой частотой 33 или 66 МГц. Габариты

данного чипа составляют 10х10 мм, он предлагается в исполнении QFP или QFN и

стоит $4,95 при заказе партии в 10 000 штук. А это значит, что каждая

материнская плата с чипсетом Intel P67, H67 и H61 и слотом PCI стоит на $4,95

дороже. Стоит отметить, что чипсеты Intel B65, Q67 и Q65 корпоративного и

бизнес-класса нативной поддержки PCI не утратили.

PCI Express — Устройство компьютера

PCI Express — бывшее название 3GIO (3D Generation Input/Output) — стандарт системной шины, продвигаемый на рынок Arapahoe Working Group (также называемой Arapahoe Special Interest Group (Arapahoe SIG)). Важным фактором, влияющим на продвижение этой архитектуры, является то, что входящие в Arapahoe SIG компании входили также и в PCI SIG и принимали активное участие в разработках шины PCI. Роджер Тайпли (Roger Tipley), президент PCI SIG, заявил, что переход с шины PCI на шину Arapahoe должен произойти так же плавно, как произошел переход с ISA на PCI. Столь самоуверенное заявление должно иметь под собой твердую почву. Давайте рассмотрим шину PCI Express и ее преимущества перед другими технологиями.

Роджер Тайпли (Roger Tipley), президент PCI SIG, заявил, что переход с шины PCI на шину Arapahoe должен произойти так же плавно, как произошел переход с ISA на PCI. Столь самоуверенное заявление должно иметь под собой твердую почву. Давайте рассмотрим шину PCI Express и ее преимущества перед другими технологиями.

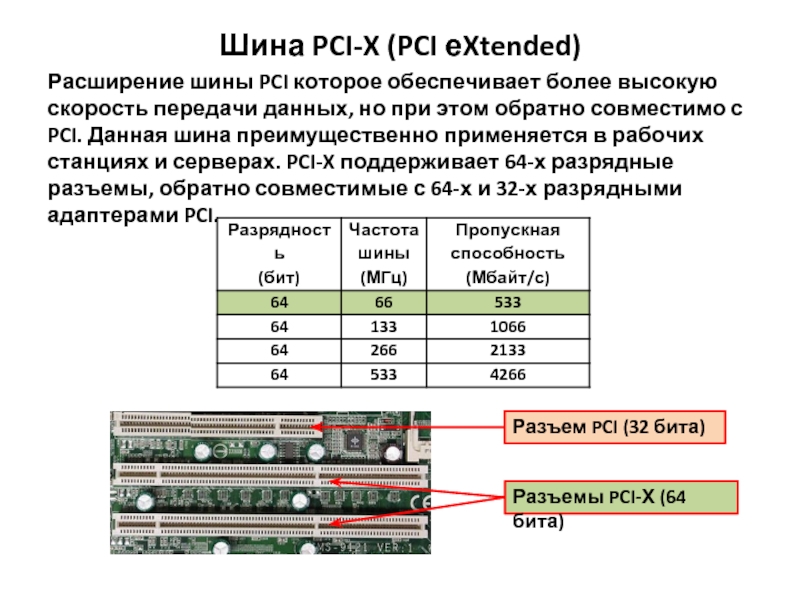

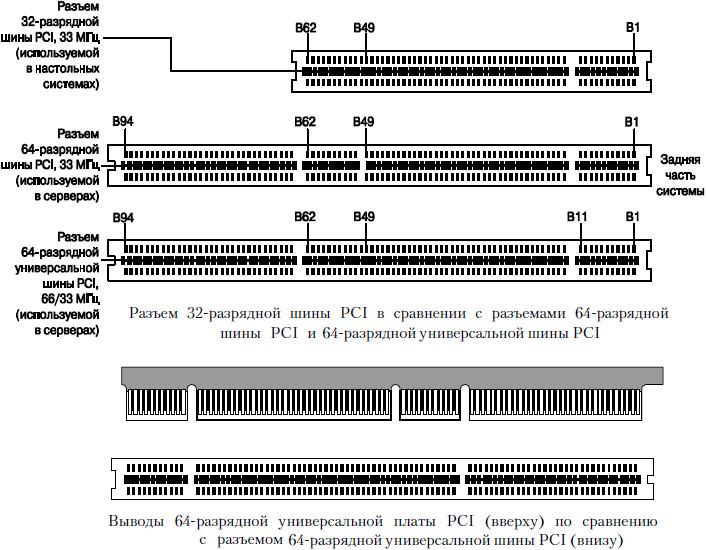

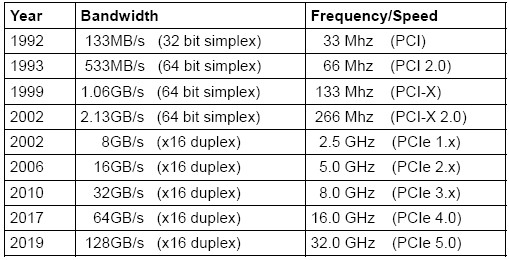

PCI Express — симметричная, двунаправленная (bi-directional) шина, которая позволяет передачу данных со скоростью до 2.5 ГБ/с, что почти в 2.5 раза больше, чем пропускная способность шины PCI-X, и более чем в 9 раз быстрее скорости работы шины PCI (мы приняли за «скорость работы PCI» значение 266 МБ/с, как среднее между двумя возможными — 133 МБ/с для 32-битовой 33-мегагерцовой и 512 МБ/с для 64-битовой 66-мегагерцовой).

Технология подключения периферийных устройств использует мост (host bridge) и несколько оконечных точек, позволяющих подключать периферийные устройства с помощью переключателя (switch). Переключатель может быть выполнен как отдельный логический элемент или интегрирован в мост. Переключатель в первую очередь предназначен для того, чтобы направлять потоки данных между периферийными устройствами, не используя мост, то есть, позволяя прямое подключение «точка-точка» (peer-to-peer). Данное решение должно меньше загружать компьютер передачей данных между конечными устройствами за счет отсутствия кэширования в памяти передаваемых данных.

Переключатель в первую очередь предназначен для того, чтобы направлять потоки данных между периферийными устройствами, не используя мост, то есть, позволяя прямое подключение «точка-точка» (peer-to-peer). Данное решение должно меньше загружать компьютер передачей данных между конечными устройствами за счет отсутствия кэширования в памяти передаваемых данных.

Огромное отличие этой шины от PCI в том, что она будет иметь изменяемую пропускную способность (scalable bandwidth). Это значит, что каждый производитель, использующий эту спецификацию, сможет наращивать пропускную способность шины или уменьшать ее в зависимости от своих потребностей, добавляя или уменьшая количество линий.

Адресация будет поддерживаться 32- и 64-битная. Каждый пакет данных будет иметь один из трех уровней приоритетов, так что система сможет разделить поток данных от периферийных устройств по приоритетам и обрабатывать данные согласно организованной в результате этого очереди.

Архитектура будет иметь три уровня организации: физический уровень, уровень данных и уровень транзакций. Уровень транзакций будет пересылать запросы на чтение и запись данных от периферийных устройств и назад, а также организовывать пакеты данных для передачи на уровень данных.

Уровень транзакций будет пересылать запросы на чтение и запись данных от периферийных устройств и назад, а также организовывать пакеты данных для передачи на уровень данных.

Одним из несомненных преимуществ стандарта Arapahoe может стать поддержка DDR RAM и Quadro DDR RAM, что позволит работать с памятью соответственно вдвое и вчетверо быстрее, чем это было ранее.

Принцип работы

Общая структура шины представлена на иллюстрации ниже:

Структура PCI Express состоит из компонентов, обычных для любой шины данных:

- Протоколы инициализации и конфигурации.

- Протоколы адресации/чтения-записи.

- Протокол передачи данных.

- Контроль циклическим, избыточным кодом (CRC).

Физическое воплощение всего вышеупомянутого — меняется в зависимости от устройства. Первые два пункта, также как у HyperTransport, соответствуют тому, что мы используем с PCI, за тем исключением, что теперь системные прерывания будут передаваться посредством виртуального MSI (Message Signaled Interrupt) вместо аппаратного сигнала по боковой полосе. Поскольку MSI является опцией в PCI 2.2, особых проблем с переходом на него возникнуть не должно. Метод контроля за ошибками также традиционен и представляет собой обычную контрольную пару бит (каждый байт информации передается как 8 бит + 2 контрольных бита = 10 бит).

Поскольку MSI является опцией в PCI 2.2, особых проблем с переходом на него возникнуть не должно. Метод контроля за ошибками также традиционен и представляет собой обычную контрольную пару бит (каждый байт информации передается как 8 бит + 2 контрольных бита = 10 бит).

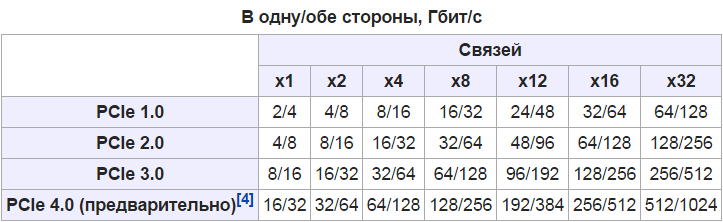

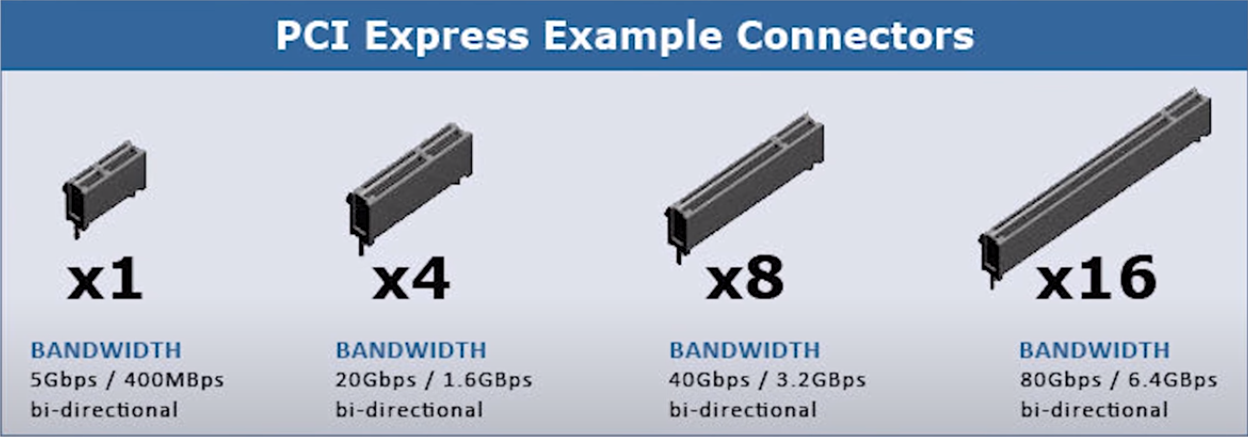

Пропускная способность и тактовая частота работы шины передачи данных PCI Express может варьироваться: клокинг увеличивается или уменьшается, магистраль, соответственно, расширяется или сужается. Первоначально на физическом уровне будет поддерживаться ширина линий х1, х2, х4, х8, х16 и х32 в одно направление. Интегрированный в системный мост или специальный коммутатор агент PCI Express эффективно распределит поток перед тем, как отправлять его по разным физическим линиям, а впоследствии, аналогичный агент соберет разные потоки данных в один, как это показано на схеме.

На данном этапе PCI SIG не декларирует тактовой частоты работы шины, ограничиваясь словами о пропускной способности в 2.5 ГБ/сек. в одном направлении при использовании 16 битной магистрали (2 по 8 бит) и 40 контактах. Путем несложных математических подсчетов можно получить частоту передачи данных примерно в 2.5 ГГц.

Путем несложных математических подсчетов можно получить частоту передачи данных примерно в 2.5 ГГц.

Именно высочайшая тактовая частота соединения должна обеспечить жизнь PCI Express на десять лет вперед. Более того, традиционное соединение PCI для дополнительных устройств будет заменено на PCI Express тогда, когда это будет необходимо. Причем новый слот будет состоять из привычного PCI гнезда (для облегчения перехода) и дополнительного коннектора.

HyperTransport

Разработка шины Lightning Data Transfer (LDT) была начата AMD в 1997 году. Несколько позже к компании из Саннивэйл присоединились такие гиганты как API Networks, Apple Computer, Cisco Systems, Nvidia, PMC-Sierra, Sun Microsystems, немного позже Transmeta и Acer Laboratories и, буквально на днях, VIA Technologies, и другие компании, образовав HyperTransport Technology Consortium. Разработка и внедрение протокола HyperTransport должно решить проблемы, связанные со скоростью, ценой, мастштабируемостью, универсальностью соединений в ПК и т. п., суть которых описана выше.

п., суть которых описана выше.

Устройства, поддерживающие протокол HyperTransport (процессоры, наборы логики, контроллеры) соединены по принципу «точка-точка» (peer-to-peer), что теоретически означает, что между собой могут быть соединены любые компоненты системы, причем без применения каких-либо коммутаторов или мостов. Каждое соединение состоит из субсоединения Передачи (Tx) и субсоединения Получения (Rx), работающих асинхронно. Передача данных организована в виде пакетов длиной до 64 байт (это значение должно быть кратно четырем). Протокол HyperTransport предполагает передачу данных по обоим фронтам сигнала.

Соединение HyperTransport может иметь магистраль шириной 2, 4, 8, 16, 32 или 64 бита в каждом направлении (Tx или Rx). Кроме того, соединения могут работать на разной тактовой частотой (от 200 до 800 МГц) в зависимости от требований к конкретному решению. Таким образом, HyperTransport предоставляет инженерам и разработчикам огромную гибкость: в случае устройств с высокими требованиями к пропускной способности (процессоры) используется пара 32-х битных соединений с частотой в 800 МГц, обеспечивающие 6. 4 ГБ/сек для Tx и 6.4 ГБ/сек для Rx соединения (результирующая линейная пропускная способность — 12.8 ГБ/сек), тогда как для сообщения между менее требовательными к скорости передачи данных компонентами (например, внутри какого-либо переносного устройства), можно задействовать четырехбитную (2 по 2 бита) магистраль, работающую на 200 МГц, что даст по 100 МБ/сек для каждого направления.

4 ГБ/сек для Tx и 6.4 ГБ/сек для Rx соединения (результирующая линейная пропускная способность — 12.8 ГБ/сек), тогда как для сообщения между менее требовательными к скорости передачи данных компонентами (например, внутри какого-либо переносного устройства), можно задействовать четырехбитную (2 по 2 бита) магистраль, работающую на 200 МГц, что даст по 100 МБ/сек для каждого направления.

Следует отметить, что устройства с разными режимами передачи данных смогут работать вместе в режиме менее быстрого. Иными словами, предполагается возможность выбора режима работы компонента. Например, устройство с шиной в 16 бит может быть подключено к устройству с режимами работы от 2 до 8 бит. Это же самое устройство может быть подключено к более быстрому, с магистралью от 32 до 64 бит.

Также необходимо упомянуть, что HyperTransport программно совместим с текущим PCI, иначе говоря, все ПО, разработанное с учетом моделей адресации и инициализации протокола PCI, будет иметь возможность функционировать и на HyperTransport платформе.

В пользу HyperTransport говорит также и относительно небольшое количество выводов, требуемых для высокой скорости передачи данных. Для примера приведем небольшую таблицу:

| Ширина шины (в каждую сторону) | 2 | 4 | 8 | 16 | 32 |

| Количество контактов для данных | 8 | 16 | 32 | 64 | 128 |

| Количество контактов для задания несущей тактовой частоты (clock pins) | 4 | 4 | 4 | 8 | 16 |

| Контрольные контакты | 4 | 4 | 4 | 4 | 4 |

| Общее количество контактов для передачи данных | 16 | 24 | 40 | 76 | 148 |

| VLDT (питание) | 2 | 2 | 3 | 6 | 10 |

| GND (заземление) | 4 | 6 | 10 | 19 | 37 |

| PWROK (power ok) | 1 | 1 | 1 | 1 | 1 |

| RESET_L (reset) | 1 | 1 | 1 | 1 | 1 |

| HyperTransport Device Stop_l (опционально, для мобильных устройств) | — | — | — | — | — |

| Devreq_l (опционально, для мобильных устройств) | — | — | — | — | — |

| Общее количество контактов | 24 | 34 | 55 | 103 | 197 |

| Пиковая пропускная способность соединения (в обе стороны) при тактовой частоте в 800 МГц | 0. 8 8 | 1.6 | 3.2 | 6.4 | 12.8 |

«—» — нет данных (судя по всему, требуется один дополнительный контакт для HyperTransport Device Stop_l и еще один для Devreq_l).

В дополнение к таблице приведем небольшую иллюстрацию:

Отметим несколько важных моментов:

- HyperTransport при 55 контактах (pins) обеспечивает в 12 раз большую пропускную способность, чем PCI 33 МГц/32 бит (более 80 контактов, правда, далеко не все используются).

- Отношение сигнал/земля — 4:1.

- Опциональные контакты, внедряемые в мобильных системах для сбережения энергии.

- Следует также упомянуть, что уровень сигнала HyperTransport составляет 1.2 Вольта при сопротивлении в 100 Ом. К слову, уровень сигнала в PCI — 3.3 вольта.

Сравнительная характеристика стандартов Arapahoe и HyperTransport

| Параметры | Arapahoe | HyperTransport |

| Симметричная/асимметричная | симметричная | асимметричная |

| Двунаправленная/однонаправленная | двунаправленная | двунаправленная |

| Скорость передачи | 2. 5 ГБ/с 5 ГБ/с | 12.8 ГБ/с |

| Peer-to-peer подключение | + | + |

| Scalable bandwidth | + | + |

| Адресация | 32- и 64-битная | 64-битная |

| Планируемый срок выхода | конец 2003 года | конец 2001 года |

Заключение

Первым набором системной логики Intel, который будет поддерживать новый интерфейс PCI Express, компания собирается выпустить осенью следующего года. В качестве рабочего имени для этого чипсета выбрано название города в штате Монтана, расположенного недалеко от ранчо главы Intel, Крейга Барретта, — «Grantsdale».

Начиная с 2004 г. корпорация намерена наладить массовый выпуск продуктов на основе технологии PCI Express: наборов микросхем и платформ уровня предприятия, настольных и мобильных систем, сетевых процессоров, полнофункциональных процессоров ввода-вывода для высокопроизводительных дисковых массивов RAID, Ethernet-адаптеров, подсистем хранения данных, а также системных плат и серверных платформ следующего поколения.

Частота PCIE

??? | Overclock.net

JavaScript отключен. Для лучшего опыта, пожалуйста, включите JavaScript в вашем браузере, прежде чем продолжить.

Частота PCIE. По умолчанию установлено значение 100 МГц, увеличение этого значения сокращает время загрузки текстур по всем направлениям (из-за более высоких скоростей передачи данных и увеличения доступной полосы пропускания по шине PCIE).

В чем недостаток разгона до 115 или 120 и в чем преимущество, помогает ли это при разгоне……

Я полагаю, что это может привести к пикселизации графики и тому подобному, но пока графика выглядит хорошо и не перегревается, все должно быть в порядке!!!!

Ответить

Сохранить

Нравится

Реакции:

1

1 — 19 из 19 сообщений

Настройка PCIe до 107-112 может улучшить стабильность в системе OCed. По некоторым данным, свыше 112 может повредить видеокарту.

Ответить

Сохранить

Нравится

Да, у меня около 107, вроде хороший район

Увидеть меньше

Узнать больше

Ответить

Сохранить

Нравится

Цитата:

| Первоначально Послано The Duke Настройка PCIe до 107-112 может улучшить стабильность в системе OCed.  По некоторым данным, свыше 112 может повредить видеокарту. По некоторым данным, свыше 112 может повредить видеокарту. |

Подъем шины PCI-E не повредит карту, однако, поскольку шины PCI-E и Sata связаны, это потенциально может привести к повреждению или отключению любых дисков Sata в системе и вызвать потерю подключения.

Как правило, не превышайте 120.

Увидеть меньше

Узнать больше

Ответить

Сохранить

Нравится

У меня стоит авто..

Ответить

Сохранить

Нравится

Цитата:

| Первоначально Послано dannyyboii У меня мой на авто.. |

120 улучшит геймплей в отношении fps, поскольку PCI -E имеет более высокую скорость шины.

Увидеть меньше

Узнать больше

Ответить

Сохранить

Как и

, я установил свою на 107 МГц

Кажется, работает нормально, что позволило мне перейти от

Частота ядра 492 МГц —> 497 МГц

Частота памяти 1,16 ГГц —> 1,18 ГГц

SLI — XFX6800XT 90 004

Ответить

Сохранить

Нравится

Цитата:

| Первоначально Послано iamme Я установил 107 МГц Кажется, работает нормально, разрешил мне перейти с Частота ядра 492 МГц —> 497 МГц SLI — XFX6800XT |

Вы пробовали использовать coolbits?

Это позволит вам разогнаться намного выше.

Увидеть меньше

Узнать больше

Ответить

Сохранить

Нравится

Реакции:

1

я не думаю, что это действительно позволяет вам работать выше, просто дает лучшую производительность, я использую для запуска на 112, и это сработало хорошо без искажений или чего-то еще,

и я думал, что это не поможет со стабильностью и может на самом деле помешать стабильности, если вы ошиблись

Ответить

Сохранить

Вроде

интересно, завтра попробую. и кстати, Asus A8N-E хороши? Я слышал, что вентилятор чипсета ломается после нескольких месяцев использования. также слышал то же самое с A8N5X. Думаю выкинуть этот мобо.

Ответить

Сохранить

Нравится

я держу свой на 110

Ответить

Сохранить

Например,

получил последние версии драйверов, и это позволило мне максимально использовать мое ядро и память

Core 700 МГц

память 2,8 ГГц

он работает, но не стабильно, поэтому я переведу шину на 110 и посмотрим, поможет ли это

оптимально, как определено на панели управления nvidia

Ядро 600 МГц

Память 2,5 ГГц

Это почти вдвое больше, просто обновив мой драйвер, и да, я использую coolbits

Увидеть меньше

Узнать больше

Ответить

Сохранить

Как и

, мне было интересно узнать об этой частоте PCI-e. У меня была система настроена на автоматический режим, когда я изменил ее на 110 МГц, я не заметил никаких изменений или увеличения стабильности. Оценка 3DMark ТОЧНО такая же.

У меня была система настроена на автоматический режим, когда я изменил ее на 110 МГц, я не заметил никаких изменений или увеличения стабильности. Оценка 3DMark ТОЧНО такая же.

Единственное, что я предполагаю, это то, что это позволяет немного повысить способность OC.

Ответить

Сохранить

Нравится

Этой теме уже два года, начни новую дружище.

И да, обычно это просто обеспечивает лучшую стабильность и, как правило, только в системах AMD.

Ответить

Сохранить

Например,

Ну, поскольку это было изменено, я мог бы также добавить/уточнить…

Увеличение частоты PCIE только увеличивает частоту шины… информация, передаваемая туда и обратно от видеокарты, никогда не потребует так много скорость, поэтому ее увеличение не дает повышения производительности/стабильности… на самом деле, есть шанс повредить карту и/или материнскую плату…

Если вы хотите в виде аналогии:

У вас есть

3 автомобиля со скоростью 55 миль в час по 4-полосному шоссе

Будет ли это отличаться от

3 автомобиля со скоростью 55 миль в час по 6-полосному шоссе?

НЕТ!

Увидеть меньше

Узнать больше

Ответить

Сохранить

Например,

Похоже, этот эффект работал на наборе микросхем NF4. .. кроме этого понятия не имею.

.. кроме этого понятия не имею.

Могу точно сказать, это улучшило мою разгонку на DFI SLI-DR 939 МБ!

Ответить

Сохранить

Нравится

Цитата:

| Первоначально написал killa_concept У вас есть 3 машины, которые едут со скоростью 55 миль в час по 4-полосному шоссе Будет ли это отличаться от 3 машины, которые едут 55 миль в час по 6-полосному шоссе? |

На самом деле да, разница есть. Поскольку остальные люди на шоссе едут с нормальной скоростью 75 миль в час, им в конечном итоге придется обогнать этих трех парней. Большинство людей (по крайней мере, там, где я живу), которые ездят так медленно по шоссе, даже не заботятся о том, чтобы посмотреть в зеркало заднего вида, чтобы увидеть, не хочет ли кто-нибудь еще их обогнать, поэтому остальным людям придется втиснуть себя. в единственную оставшуюся полосу, создавая хорошую пробку. На 6-полосной трассе пробка не такая страшная.

Это относится и к шине PCIE. Правильная аналогия:

Если три автомобиля движутся со скоростью 55 миль в час по 3-полосному шоссе, они вызовут большую пробку позади себя, чем если бы они двигались со скоростью 65 миль в час.

Вся идея увеличения пропускной способности PCIE заключается не в том, что видеокарты передают 4 ГБ данных каждую секунду КАЖДУЮ секунду (стандартная скорость), а в том, что когда картам требуется пакет данных (вещи в оперативной памяти, которые не вписываются в текстуру память), это будет происходить быстрее, создавая меньше узких мест для всех других передач данных, которые он должен выполнять.

Увидеть меньше

Узнать больше

Ответить

Сохранить

Нравится

Возрождение Святой Нити Бэтмен!

Увидеть меньше

Узнать больше

Ответить

Сохранить

Например,

эй, ребята, у меня частота моего ПК составляет 117 МГц, так что теперь я хочу знать, какое должно быть дополнительное напряжение на моем PLX ??? cz Я думаю, что настройка дополнительного напряжения plx предназначена для часов pcie, верно ??? также получил напряжение ядра plx и не знаю, для чего это нужно. они оба сейчас в автоматическом режиме, но у меня произошел сбой компьютера во время теста 4k 3dmark, я пробежал 20+ на регулярной забастовке … но на 4k он разбился, поэтому я думаю, что это произошло из-за того, что aux и core plx были автоматическими. дайте мне напряжение, чтобы установить его, пожалуйста, bcz я подозреваю, что auto вкладывает в него слишком много сока, как это всегда делает auto

они оба сейчас в автоматическом режиме, но у меня произошел сбой компьютера во время теста 4k 3dmark, я пробежал 20+ на регулярной забастовке … но на 4k он разбился, поэтому я думаю, что это произошло из-за того, что aux и core plx были автоматическими. дайте мне напряжение, чтобы установить его, пожалуйста, bcz я подозреваю, что auto вкладывает в него слишком много сока, как это всегда делает auto

Ответить

Сохранить

Нравится

1 — 19 из 19 Сообщений

- Это старая тема, вы можете не получить ответ и могли

возродить старую ветку. Пожалуйста, рассмотрите возможность создания новой темы.

Верх

Как узнать скорость шины для PCIE?

JavaScript отключен. Для лучшего опыта, пожалуйста, включите JavaScript в вашем браузере, прежде чем продолжить.

Итак, я разместил вопрос о некоторых проблемах, которые у меня возникли, в другом разделе ЗДЕСЬ.

Джентльмен Написал:

Цитата:

Первоначальное сообщение от BinaryDemon

Если скорость шины PCI-e выходит далеко за пределы спецификации, это может вызвать проблемы с графическим процессором.

Нажмите, чтобы развернуть…

По сути, я пытаюсь запустить OC, и у меня стабильно работают ЦП и ОЗУ более 12 часов, но как только я запускаю что-либо, интенсивно использующее GPU, компьютер зависает или зависает (в основном зависает). На этом форуме нет ответов об этой проблеме, поэтому я решил опубликовать этот вопрос, чтобы продолжить свои знания, поскольку Google не помогает мне разобраться в этом.

Итак, чего я не понимаю, так это как определить скорость моей шины для PCIE? Я думал, что PCIE не использует шину и использует последовательные соединения. Итак, что я действительно ищу сейчас, так это то, как функция графического процессора связана с процессором. Например, когда речь идет об определении частоты процессора, вы берете FSB Clock*Multiplier. Чтобы найти частоту FSB, возьмите FSB Clock*4. Чтобы найти частоту DDR2 DRAM FSB Clock/FSBRAM. Итак, что я ищу, это X * Y = скорость шины PCIE или X / Y = скорость шины PCIE или что-то еще, или если у вас нет математической зависимости, то только сама связь; Я могу вычислить математику позже.

Ответить

Сохранить

Нравится

1 — 7 из 7 Сообщений

То, о чем вы говорите, не является скоростью автобуса. Это скорость, с которой работает компонент, подключенный к шине.

PCIe:

Одна линия PCIe 1.0 (или 1.1) может одновременно передавать до 2,5 гигатранзакций в секунду (ГТ/с) в каждом направлении. Для PCIe 2.0 эта скорость увеличивается до 5 ГТ/с, а одна линия PCIe 3.0 может передавать 8 ГТ/с.

Фактический объем данных, проходящих через шину PBIe, зависит от скорости подключенного к ней компонента.

Ответить

Сохранить

Вроде

Хорошо, это действительно ничего не объясняло и не имело никакого смысла. Я не спрашивал, сколько данных передается через мою шину PCIE.

В общем, чувак сказал мне проверить скорость шины PCIE, она может быть слишком высокой. Насколько мне известно, PCIE не использует шину, они используют последовательные соединения, обычно называемые полосами. Итак, поскольку я только что увеличил тактовую частоту FSB, чтобы увеличить частоту процессора, как это увеличит мою «скорость шины PCIE», также известную как последовательное соединение, которое обычно составляет 100 МГц, если только оно не было преднамеренно OC’d.

Серьезно, я только что присоединился к этому форуму, я не просто ленюсь и говорю: «Это мои системные характеристики, какие спецификации использовать?» Я ХОЧУ это узнать, уже сутками пытаюсь разобраться как все работает по отношению друг к другу, т.е. если я это сделаю то это повлияет на это и на это все не спрашивая , как и должно быть. Я столкнулся с чем-то, о чем Google не знает, спросите здесь и получите копию и вставку из Википедии, которая не имеет ничего общего с моим вопросом.

Увидеть меньше

Узнать больше

Ответить

Сохранить

Нравится

Цитата:

Первоначально Послано Meniscus

Так что я не понимаю, как мне определить, что моя скорость шины для PCIE? Я думал, что PCIE не использует шину и использует последовательные соединения.

Нажмите, чтобы развернуть…

Цитата:

Первоначальное сообщение от BinaryDemon

Если скорость шины PCI-e выходит далеко за пределы спецификации, это может вызвать проблемы с графическим процессором.

Нажмите, чтобы развернуть…

Вы не можете (не можете) установить скорость шины. Скорость шины определяется международным комитетом по спецификациям (PCI-SIG) и конструкцией материнской платы. Все, что вы можете изменить, это объем данных, которые вы пытаетесь отправить по шине. Разгон (изменение множителей, тактовых частот и скоростей шины) изменяет только скорость устройства, подключенного к шине, а не базовую скорость шины. Последовательное соединение — это просто соединение через шину последовательного типа. Полосы — это просто количество отдельных подключений к шине, доступных для устройства.

Скорость автобуса очень похожа на ограничение скорости на шоссе. Если шоссе в час пик забивается, мы с вами ничего не можем сделать, чтобы увеличить ограничение скорости, чтобы позволить проехать большему количеству автомобилей. Это могут сделать только сильные мира сего, правительство (то есть разработчики материнских плат).

Этот джентльмен не говорит ускорить автобус (т. е. изменить ограничение скорости), он предполагает, что вы пытаетесь отправить через автобус больше данных (больше автомобилей), чем он может обработать.

е. изменить ограничение скорости), он предполагает, что вы пытаетесь отправить через автобус больше данных (больше автомобилей), чем он может обработать.

Я быстро поискал в Google схемы материнских плат, на которых указаны скорости шины.

Возможно, вы сможете найти его для вашей материнской платы.

Кроме того, зависания обычно вызваны проблемами с памятью, памятью графического процессора или памяти компьютера.

Увидеть меньше

Узнать больше

Ответить

Сохранить

Например,

Вы должны стараться поддерживать скорость шины PCIE на уровне 100 МГц, все, что выше, может вызвать нестабильность системы. Должна быть настройка BIOS, чтобы вы могли заблокировать его на 100.

Ответить

Сохранить

Как и

, в вашем биосе будет возможность изменить частоту PCI-E, на складе это 100 МГц и должна оставаться на этой скорости, поскольку нет никакой реальной причины ее повышать.

Ответить

Сохранить

Как и

, частота PCIe не имеет ничего общего с тем, сколько данных может обрабатывать шина PCIe. Это связано с целостностью данных, проходящих через шину. Это не означает, что изменение частоты PCIe не приведет к более высокому разгону, это просто зависит от того, почему разгон не работает (ошибки выдачи видеокарты или повреждение данных в шине).

Это связано с целостностью данных, проходящих через шину. Это не означает, что изменение частоты PCIe не приведет к более высокому разгону, это просто зависит от того, почему разгон не работает (ошибки выдачи видеокарты или повреждение данных в шине).

Не совсем точно, но объясняет вышесказанное:

Синяя трасса: идеальные часы с расширенным спектром PCI Express (частота никогда не превышает 100 МГц).

Красная трасса: 0,5% тактового сигнала PCI Express с разбросом по центру. .. максимальная тактовая частота достигает 100,2 МГц, что превышает ограничение максимальной частоты в 100 МГц.

Коричневая кривая: тактовая частота PCI Express с разбросом по центру 1%. Эти часы нарушают спецификацию PCI Express i

Зеленая трасса: часы PCI Express с постоянной частотой 100,1 МГц. Эти часы нарушают спецификацию PCI Express 9.0050 Розовые маркеры: допуск 300 ppm на частоте около 100 МГц, разрешенный спецификацией PCI Express. Тактовая частота не должна превышать верхнюю розовую метку.

1

1