Pci 1 шина: Страшные сказки на ночь, о PCI шине / Хабр

Содержание

Страшные сказки на ночь, о PCI шине / Хабр

Всеобщая эйфория от появления на рынке новых процессоров, не дает достаточно времени кинуть взгляд, а что же там у них «под капотом». Те же их стороны, которыми обычно восхищаются

кликатели и кнопкодавы

, вовсе не отражают реальное положение дел на железном фронте.

А тучи, тем временем, сгущались. Да, процессоры стали быстрее. Да, действительно, там стало больше ядер. И последнее, как раз, является серьезной архитектурной проблемой. По крайней мере, для наметившегося лидера гонки.

Кто сейчас помнит такой архаизм как «Архитектура»? Мало кто. Слово в станкостроении стало в IT практически ругательным. А ведь когда-то, в былые времена, книга «PCI System Architecture „ и прочие, зачитывалась до дыр, на экране. И что же там такого страшного, в этом осколке прошлого, накарябано о PCI, что может нас ввести в глубокую задумчивость, полную вселенской грусти?

Страшная цифра — 256. Хотя, на первый взгляд, и не очень страшная. Да, именно столько, и есть максимальный предел присутствия независимых PCI устройств, на PCI шине. Цифра кажется на самом деле заоблачной.

Хотя, на первый взгляд, и не очень страшная. Да, именно столько, и есть максимальный предел присутствия независимых PCI устройств, на PCI шине. Цифра кажется на самом деле заоблачной.

Ну кому, в здравом уме и твердой памяти, придет в голову иметь в компьютере больше 5-10 реальных, т.е. “физических» устройств? Именно исходя из этих «логичных» предпосылок, недавний лидер процессорной гонки, вводил ограничивающие настройки в свой чипсет, дающие возможность принудительно ограничивать волшебную цифру до 128, 64, и не поверите 32(!) PCI шин. И это была не просто блажь, т.к. давало серьезную возможность экономить системный кусок (первые 4Gb) памяти, до сих пор наделенный «волшебными свойствами» в отношении ОС. В том то и дело, что физических устройств было до недавнего времени не очень много.

Но, время не стоит на месте, и вот я держу в руках очередное 64 ядерное чудо враждебной техники, Rome от AMD.

И что же он хочет, нет ТРЕБУЕТ, для своего минимального функционирования? Всего то малость… откусить для своих 64 ядер… пространство в 80 PCI шин. Браво. Но, ведь у нас есть еще 2/3 пространства? У кого то есть, а у кого-то и нет.

Браво. Но, ведь у нас есть еще 2/3 пространства? У кого то есть, а у кого-то и нет.

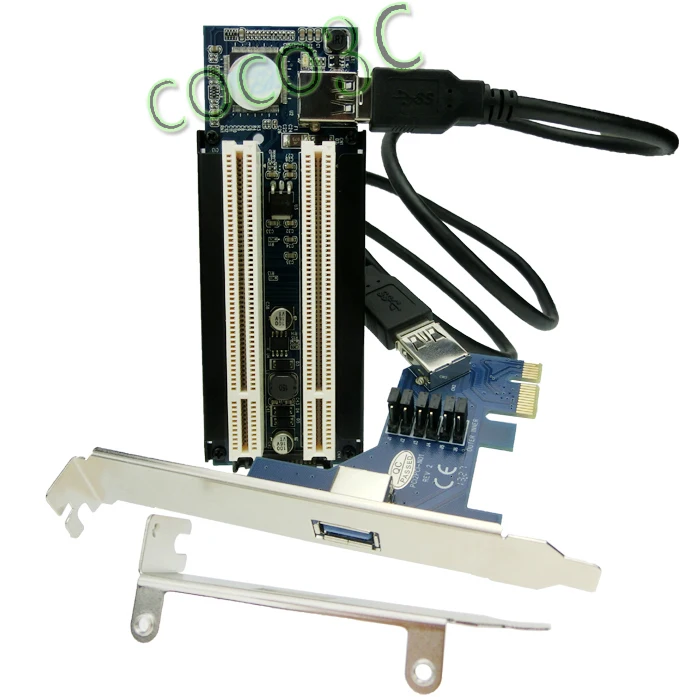

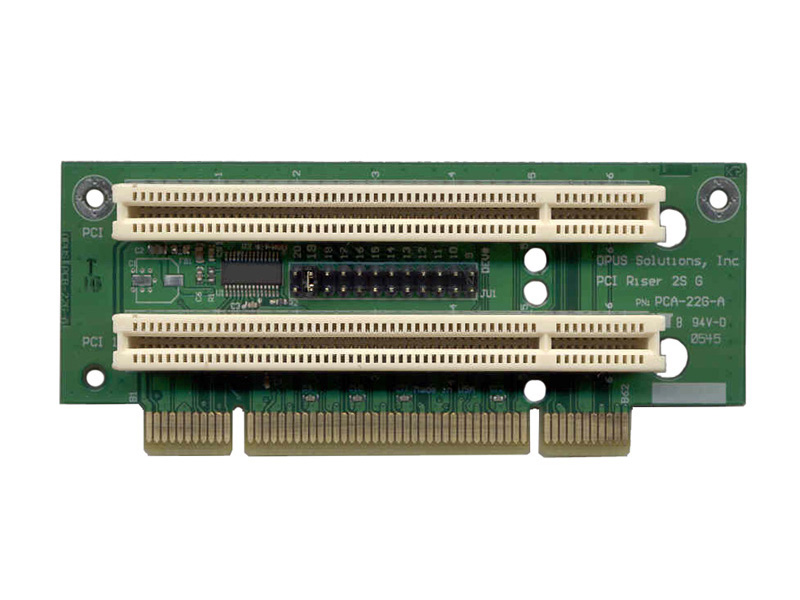

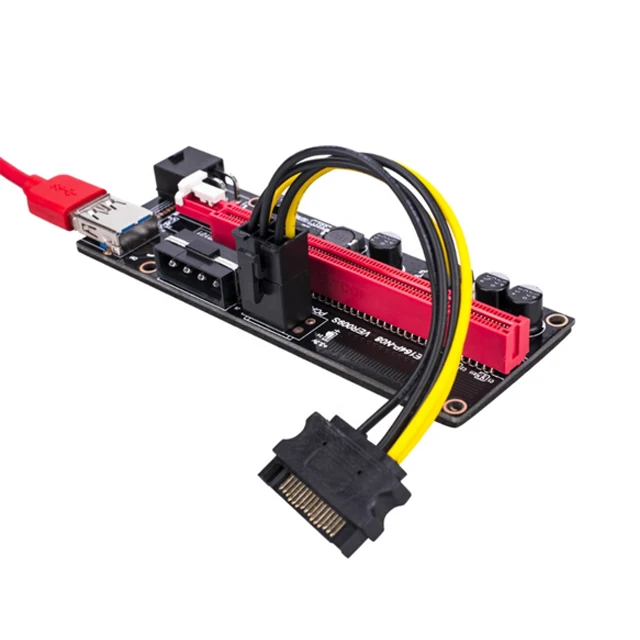

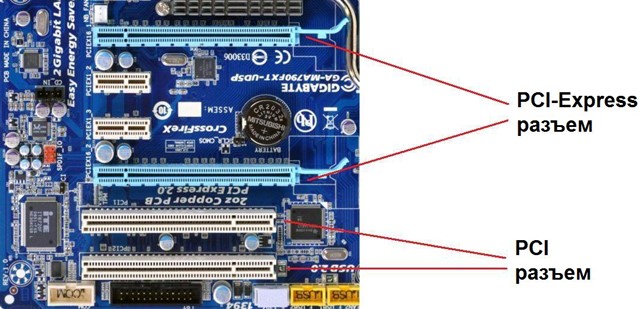

Первый раз на небездонность PCI шины я обратил внимание, настраивая PCI расширитель, так уж получилось, что на нем висело, за гроздью из P2P мостов Pericom, 119 PCI устройств требовавших подобное же количество индивидуальных PCI шин. И это только за единственным х8 PCI расширителем. А таких х8 портов, там было 8. Вот тут, как бы невзначай, и всплывает «волшебность» первых 4Gb системной памяти, когда львиная доля из тех 119 PCI устройств, требует для своей инициализации во время обнаружения БИОСом «скромные» 32-64 Мб на каждого.

Хорошо что Интел не так мощно выгрызет PCI пространство. При необходимости, но повесить второю гроздь еще оставалось возможным.

А вот с Rome и единственное такое «расширение» лишает нас надежды хоть на какое то будущее столь увесистой «грозди», в этой АМД системе. Нет, конечно, клиенту можно предложить перейти на суперкомпьютерную архитектуру, ту которая будет под заказ, и выльется в 10 раз дороже. Но и вышепредложенная конфигурация, как вы успели заметить, не для каждого из нас. И также разрабатывается индивидуально под хотелки клиента. Но архитектурная граница хотелок уже ощутимо близка. Не хочется в каждую вышку мобильной связи лепить суперкомпьютер, исключительно из-за тридцатилетней «ограниченности» PCI шины. Что самое интересное, но переход на ARM совершенно не выход, поскольку на нем мы видим все тот же PCI, и все те же 30 летние ограничения.

Но и вышепредложенная конфигурация, как вы успели заметить, не для каждого из нас. И также разрабатывается индивидуально под хотелки клиента. Но архитектурная граница хотелок уже ощутимо близка. Не хочется в каждую вышку мобильной связи лепить суперкомпьютер, исключительно из-за тридцатилетней «ограниченности» PCI шины. Что самое интересное, но переход на ARM совершенно не выход, поскольку на нем мы видим все тот же PCI, и все те же 30 летние ограничения.

Увы, ситуация в деталях повторяет тенденцию с памятью, стало мало? Пихай-суй больше! PCI пространство есть? Что его жалеть, от него не убудет. Увы, уже убудет. Уже, не то что в четверо или вдвое не обрежешь, чем баловался Интел. Уже и в полном объеме, для серьезных игроков — на грани. И применение транспарентных P2P мостов, увы только паллиатив, в сложившейся ситуации.

Только и остается что беречь каждый байт адрес шины. Или мечтать о том что крупные игроки созреют для создания IP6 адресов SuperPCIExpress.

UPD

Уважаемый ikle, поделился ценной информацией по поднятой теме в своем комментарии

Дак в PCI всё для этого уже есть — буковка S в SBDF — целых 16 бит — четвёртое измерение. Более того, PCI-E позволяет уже использовать разные сегменты: Если ОС не дремучая и умеет понимать ACPI MCFG таблицу, то проблемы никакой нет уже сейчас.

Описываемая в статье проблема — это проблема реализации платформы: никто не мешает прямо сейчас завести на платформе несколько сегментов, подправить BIOS, чтобы он отдавал в ACPI MCFG, где искать базовый каждого адрес сегмента и всё

А от себя добавлю, что в UefiShell есть коменда pci c параметром -s Seg которая как раз и показывет нужный PCI сегмент. Печаль только в том, что новые сегменты растут исключительно(я так пока понял) из дополнительных физических процессоров. А с этим мало кто встречается. Многоядерность — «это не совсем то». Либо, как вариант, P2P мост должен поддерживать эту достаточно не популярную в широких массах опцию.

UPD2

Всем, сигнализировавшим от ошибках в тексте, большое спасибо. Исправил, как только смог.

Общие сведения о PCI — Windows drivers

-

Статья -

- Чтение занимает 4 мин

-

Общие сведения о технологии Pci.

Технология Pci не связана ни с какими заголовками.

Перечисления

| NPEM_CONTROL_STANDARD_CONTROL_BIT Дополнительные сведения: NPEM_CONTROL_STANDARD_CONTROL_BIT |

Функции

| ENABLE_VIRTUALIZATION Подпрограмма EnableVirtualization включает или отключает виртуализацию для устройства PCI Express (PCIe), поддерживающего интерфейс виртуализации с одним корневым интерфейсом ввода-вывода (SR-IOV). |

| GET_VIRTUAL_DEVICE_DATA Подпрограмма GetVirtualFunctionData считывает данные из пространства конфигурации PCI Express (PCIe) виртуальной функции (VF) на устройстве, поддерживающем единый корневой интерфейс виртуализации ввода-вывода (SR-IOV). |

| GET_VIRTUAL_DEVICE_LOCATION Подпрограмма GetLocation возвращает расположение устройства виртуальной функции PCI Express (PCIe) на шине PCI. Устройство, поддерживающее единый корневой интерфейс виртуализации ввода-вывода (SR-IOV), может предоставлять одну или несколько виртуальных машин на шине PCI. |

| GET_VIRTUAL_DEVICE_RESOURCES Подпрограмма GetResources возвращает ресурсы, необходимые физической функции PCI Express (PCIe) для включения виртуализации на устройстве, поддерживающем интерфейс виртуализации с одним корневым интерфейсом ввода-вывода (SR-IOV). |

| GET_VIRTUAL_FUNCTION_PROBED_BARS Подпрограмма GetVirtualFunctionProbedBars возвращает значения базовых регистров адресов PCI Express (PCIe) устройства, поддерживающего единый корневой интерфейс виртуализации ввода-вывода (SR-IOV). |

| NPEM_CONTROL_ENABLE_DISABLE Дополнительные сведения: NPEM_CONTROL_ENABLE_DISABLE |

| NPEM_CONTROL_QUERY_STANDARD_CAPABILITIES Дополнительные сведения: NPEM_CONTROL_QUERY_STANDARD_CAPABILITIES |

| NPEM_CONTROL_SET_STANDARD_CONTROL Дополнительные сведения: NPEM_CONTROL_SET_STANDARD_CONTROL |

| SET_VIRTUAL_DEVICE_DATA Подпрограмма SetVirtualFunctionData записывает данные в пространство конфигурации PCI Express (PCIe) виртуальной функции (VF) на устройстве, поддерживающем единый корневой интерфейс виртуализации ввода-вывода (SR-IOV). |

Структуры

| NPEM_CAPABILITY_STANDARD Дополнительные сведения: NPEM_CAPABILITY_STANDARD |

| NPEM_CONTROL_INTERFACE Дополнительные сведения: NPEM_CONTROL_INTERFACE |

| PCI_CAPABILITIES_HEADER Структура _PCI_CAPABILITIES_HEADER (wdm.h) определяет заголовок, который присутствует в каждой структуре возможностей PCI. |

| PCI_DEVICE_PRESENT_INTERFACE Структура PCI_DEVICE_PRESENT_INTERFACE зарезервирована для использования системой. |

| PCI_EXPRESS_AER_CAPABILITIES Структура _PCI_EXPRESS_AER_CAPABILITIES (wdm.h) описывает расширенные возможности ошибок PCI Express (PCIe) и регистр управления. |

| PCI_EXPRESS_AER_CAPABILITY Структура _PCI_EXPRESS_AER_CAPABILITY (wdm.h) описывает расширенную структуру отчетов об ошибках PCI Express (PCIe). |

| PCI_EXPRESS_BRIDGE_AER_CAPABILITY Структура _PCI_EXPRESS_BRIDGE_AER_CAPABILITY (wdm.h) определяет расширенные возможности отчетов об ошибках PCI Express (PCIe) для устройства моста PCIe. |

| PCI_EXPRESS_CAPABILITIES_REGISTER Структура _PCI_EXPRESS_CAPABILITIES_REGISTER (ntddk.h) описывает регистр возможностей PCI Express (PCIe) структуры возможностей PCIe. |

| PCI_EXPRESS_CAPABILITY Структура PCI_EXPRESS_CAPABILITY описывает структуру возможностей PCI Express (PCIe). |

| PCI_EXPRESS_CORRECTABLE_ERROR_MASK Структура _PCI_EXPRESS_CORRECTABLE_ERROR_MASK (wdm.h) описывает регистр маски ошибок, допускающий исправление PCI Express (PCIe), используемый в расширенных отчетах об ошибках. |

| PCI_EXPRESS_CORRECTABLE_ERROR_STATUS Структура _PCI_EXPRESS_CORRECTABLE_ERROR_STATUS (wdm.h) описывает регистр исправляемых ошибок PCI Express (PCIe) для расширенного создания отчетов об ошибках. |

| PCI_EXPRESS_DESIGNATED_VENDOR_SPECIFIC_CAPABILITY Представляет расширенную возможность определенного поставщика, определяемую PCI-SIG. |

| PCI_EXPRESS_DESIGNATED_VENDOR_SPECIFIC_HEADER_1 Представляет заголовок расширенных возможностей, зависящий от определенного поставщика, определенный PCI-SIG. |

| PCI_EXPRESS_DESIGNATED_VENDOR_SPECIFIC_HEADER_2 Представляет заголовок расширенной возможности для определенного поставщика 2, определенный PCI-SIG. |

| PCI_EXPRESS_DEVICE_CAPABILITIES_REGISTER Структура _PCI_EXPRESS_DEVICE_CAPABILITIES_REGISTER (ntddk. |

| PCI_EXPRESS_DEVICE_CONTROL_REGISTER Структура _PCI_EXPRESS_DEVICE_CONTROL_REGISTER (ntddk.h) описывает регистр управления устройствами PCI Express (PCIe) структуры возможностей PCIe. |

| PCI_EXPRESS_DEVICE_STATUS_REGISTER Структура _PCI_EXPRESS_DEVICE_STATUS_REGISTER (ntddk.h) описывает регистр состояния устройства PCI Express (PCIe) структуры возможностей PCIe. |

| PCI_EXPRESS_DPC_CAPABILITY Дополнительные сведения: PCI_EXPRESS_DPC_CAPABILITY |

| PCI_EXPRESS_DPC_CAPS_REGISTER Дополнительные сведения: PCI_EXPRESS_DPC_CAPS_REGISTER |

| PCI_EXPRESS_DPC_CONTROL_REGISTER Дополнительные сведения: PCI_EXPRESS_DPC_CONTROL_REGISTER |

| PCI_EXPRESS_DPC_ERROR_SOURCE_ID Структура PCI_EXPRESS_DPC_ERROR_SOURCE_ID… |

| PCI_EXPRESS_DPC_RP_PIO_EXCEPTION_REGISTER Дополнительные сведения: PCI_EXPRESS_DPC_RP_PIO_EXCEPTION_REGISTER |

| PCI_EXPRESS_DPC_RP_PIO_HEADERLOG_REGISTER Дополнительные сведения: PCI_EXPRESS_DPC_RP_PIO_HEADERLOG_REGISTER |

| PCI_EXPRESS_DPC_RP_PIO_IMPSPECLOG_REGISTER Дополнительные сведения: PCI_EXPRESS_DPC_RP_PIO_IMPSPECLOG_REGISTER |

| PCI_EXPRESS_DPC_RP_PIO_MASK_REGISTER Дополнительные сведения: PCI_EXPRESS_DPC_RP_PIO_MASK_REGISTER |

| PCI_EXPRESS_DPC_RP_PIO_SEVERITY_REGISTER Дополнительные сведения: PCI_EXPRESS_DPC_RP_PIO_SEVERITY_REGISTER |

| PCI_EXPRESS_DPC_RP_PIO_STATUS_REGISTER Дополнительные сведения: PCI_EXPRESS_DPC_RP_PIO_STATUS_REGISTER |

| PCI_EXPRESS_DPC_RP_PIO_SYSERR_REGISTER Дополнительные сведения: PCI_EXPRESS_DPC_RP_PIO_SYSERR_REGISTER |

| PCI_EXPRESS_DPC_RP_PIO_TLPPREFIXLOG_REGISTER Дополнительные сведения: PCI_EXPRESS_DPC_RP_PIO_TLPPREFIXLOG_REGISTER |

| PCI_EXPRESS_DPC_STATUS_REGISTER Дополнительные сведения: PCI_EXPRESS_DPC_STATUS_REGISTER |

| PCI_EXPRESS_ENHANCED_CAPABILITY_HEADER Структура _PCI_EXPRESS_ENHANCED_CAPABILITY_HEADER (wdm. |

| PCI_EXPRESS_ERROR_SOURCE_ID Структура _PCI_EXPRESS_ERROR_SOURCE_ID (wdm.h) описывает идентификаторы первой исправляемой и первой незаменяемой ошибки в регистре состояния ошибки. |

| PCI_EXPRESS_LANE_ERROR_STATUS Дополнительные сведения: PCI_EXPRESS_LANE_ERROR_STATUS |

| PCI_EXPRESS_LINK_CAPABILITIES_REGISTER Структура _PCI_EXPRESS_LINK_CAPABILITIES_REGISTER (ntddk.h) описывает возможности связи PCI Express (PCIe) со структурой возможностей PCIe. |

| PCI_EXPRESS_LINK_CONTROL_REGISTER Структура _PCI_EXPRESS_LINK_CONTROL_REGISTER (ntddk.h) описывает регистр управления связью PCI Express (PCIe) структуры возможностей PCIe. |

| PCI_EXPRESS_LINK_CONTROL3 Дополнительные сведения: PCI_EXPRESS_LINK_CONTROL3 |

| PCI_EXPRESS_LINK_QUIESCENT_INTERFACE Структура PCI_EXPRESS_LINK_QUIESCENT_INTERFACE зарезервирована для использования системы. |

| PCI_EXPRESS_LINK_STATUS_REGISTER Структура _PCI_EXPRESS_LINK_STATUS_REGISTER (ntddk.h) описывает регистр состояния связи PCI Express (PCIe) структуры возможностей PCIe. |

| PCI_EXPRESS_NPEM_CAPABILITY Дополнительные сведения: PCI_EXPRESS_NPEM_CAPABILITY |

| PCI_EXPRESS_NPEM_CAPABILITY_REGISTER Дополнительные сведения: PCI_EXPRESS_NPEM_CAPABILITY_REGISTER |

| PCI_EXPRESS_NPEM_CONTROL_REGISTER Дополнительные сведения: PCI_EXPRESS_NPEM_CONTROL_REGISTER |

| PCI_EXPRESS_NPEM_STATUS_REGISTER Дополнительные сведения: PCI_EXPRESS_NPEM_STATUS_REGISTER |

| PCI_EXPRESS_PME_REQUESTOR_ID Структура _PCI_EXPRESS_PME_REQUESTOR_ID (ntddk.h) описывает идентификатор запрашивающего события управления питанием (PME). |

| PCI_EXPRESS_PTM_CAPABILITY Зарезервировано для PCI_EXPRESS_PTM_CAPABILITY. Не используйте. |

| PCI_EXPRESS_PTM_CAPABILITY_REGISTER Зарезервировано для PCI_EXPRESS_PTM_CAPABILITY_REGISTER. |

| PCI_EXPRESS_PTM_CONTROL_REGISTER Зарезервировано для PCI_EXPRESS_PTM_CONTROL_REGISTER. Не используйте. |

| PCI_EXPRESS_ROOT_CAPABILITIES_REGISTER Структура _PCI_EXPRESS_ROOT_CAPABILITIES_REGISTER (ntddk.h) описывает корневой регистр возможностей PCI Express (PCIe) структуры возможностей PCIe. |

| PCI_EXPRESS_ROOT_CONTROL_REGISTER Структура _PCI_EXPRESS_ROOT_CONTROL_REGISTER (ntddk.h) описывает корневой регистр управления PCI Express (PCIe) структуры возможностей PCIe. |

| PCI_EXPRESS_ROOT_ERROR_COMMAND Структура _PCI_EXPRESS_ROOT_ERROR_COMMAND (wdm.h) описывает корневую команду ошибки PCI Express (PCIe) для расширенного создания отчетов об ошибках. |

| PCI_EXPRESS_ROOT_ERROR_STATUS Структура _PCI_EXPRESS_ROOT_ERROR_STATUS (wdm.h) описывает регистр корневой ошибки PCI Express (PCIe) для расширенного создания отчетов об ошибках. |

| PCI_EXPRESS_ROOT_PORT_INTERFACE Структура PCI_EXPRESS_ROOT_PORT_INTERFACE зарезервирована для использования системы. |

| PCI_EXPRESS_ROOT_STATUS_REGISTER Структура _PCI_EXPRESS_ROOT_STATUS_REGISTER (ntddk.h) описывает корневой регистр состояния PCI Express (PCIe) структуры возможностей PCIe. |

| PCI_EXPRESS_ROOTPORT_AER_CAPABILITY Структура _PCI_EXPRESS_ROOTPORT_AER_CAPABILITY (wdm.h) описывает расширенную структуру отчетов об ошибках PCI Express (PCIe). |

| PCI_EXPRESS_SEC_AER_CAPABILITIES Структура _PCI_EXPRESS_SEC_AER_CAPABILITIES (wdm.h) описывает дополнительные возможности ошибок PCI Express (PCIe) и регистр управления. |

| PCI_EXPRESS_SEC_UNCORRECTABLE_ERROR_MASK Структура _PCI_EXPRESS_SEC_UNCORRECTABLE_ERROR_MASK (wdm.h) описывает вторичный регистр маски незаменяемых ошибок PCI Express (PCIe). |

| PCI_EXPRESS_SEC_UNCORRECTABLE_ERROR_SEVERITY Структура _PCI_EXPRESS_SEC_UNCORRECTABLE_ERROR_SEVERITY (wdm.h) описывает вторичный регистр серьезности ошибок, неуправляемый в PCI Express (PCIe). |

| PCI_EXPRESS_SEC_UNCORRECTABLE_ERROR_STATUS Структура _PCI_EXPRESS_SEC_UNCORRECTABLE_ERROR_STATUS (wdm. |

| PCI_EXPRESS_SECONDARY_CAPABILITY Дополнительные сведения: PCI_EXPRESS_SECONDARY_CAPABILITY |

| PCI_EXPRESS_SERIAL_NUMBER_CAPABILITY Структура _PCI_EXPRESS_SERIAL_NUMBER_CAPABILITY (wdm.h) описывает серийный номер для устройства PCI Express (PCIe). |

| PCI_EXPRESS_SLOT_CAPABILITIES_REGISTER Структура _PCI_EXPRESS_SLOT_CAPABILITIES_REGISTER (ntddk.h) описывает регистр возможностей слота PCI Express (PCIe). |

| PCI_EXPRESS_SLOT_CONTROL_REGISTER Структура _PCI_EXPRESS_SLOT_CONTROL_REGISTER (ntddk.h) описывает регистр управления слотом PCI Express (PCIe). |

| PCI_EXPRESS_SLOT_STATUS_REGISTER Структура _PCI_EXPRESS_SLOT_STATUS_REGISTER (ntddk.h) описывает регистр состояния слота PCI Express (PCIe). |

| PCI_EXPRESS_UNCORRECTABLE_ERROR_MASK Структура _PCI_EXPRESS_UNCORRECTABLE_ERROR_MASK (wdm. |

| PCI_EXPRESS_UNCORRECTABLE_ERROR_SEVERITY Структура _PCI_EXPRESS_UNCORRECTABLE_ERROR_SEVERITY (wdm.h) описывает регистр серьезности ошибки PCI Express (PCIe). |

| PCI_EXPRESS_UNCORRECTABLE_ERROR_STATUS Структура _PCI_EXPRESS_UNCORRECTABLE_ERROR_STATUS (wdm.h) описывает регистр состояния незаменяемой ошибки PCI Express (PCIe). |

| PCI_FPB_CAPABILITIES_REGISTER Регистрация возможностей моста моста портала с плоской (FPB). См. раздел 7.y.2. |

| PCI_FPB_CAPABILITY Возможности моста с плоской портала (FPB), необходимые для любой функции моста, реализующей FPB. См. раздел 7.y. |

| PCI_FPB_CAPABILITY_HEADER Заголовок ППВМ . См. раздел 7.y.1. |

| PCI_FPB_MEM_HIGH_VECTOR_CONTROL1_REGISTER Регистр ППВМ MEM с высоким вектором 1. См. раздел 7.y.6. |

| PCI_FPB_MEM_HIGH_VECTOR_CONTROL2_REGISTER Регистр FPB MEM High Vector Control 2. |

| PCI_FPB_MEM_LOW_VECTOR_CONTROL_REGISTER FPB MEM Low Vector Control Register. См. раздел 7.y.5. |

| PCI_FPB_RID_VECTOR_CONTROL1_REGISTER Регистр вектора RID FPB 1. См. раздел 7.y.3. |

| PCI_FPB_RID_VECTOR_CONTROL2_REGISTER Узнайте о регистре векторного элемента управления FPB RID 1. См. раздел 7.y.3. |

| PCI_FPB_VECTOR_ACCESS_CONTROL_REGISTER Регистр контроль доступа вектора FPB. См. раздел 7.y.8. |

| PCI_FPB_VECTOR_ACCESS_DATA_REGISTER Регистр данных доступа к вектору FPB. См. раздел 7.y.9. |

| PCI_PM_CAPABILITY Структура _PCI_PM_CAPABILITY (wdm.h) содержит поля, описывающие возможности управления питанием устройства. |

| PCI_PMC Структура _PCI_PMC (wdm.h) описывает содержимое регистра возможностей управления питанием. |

| PCI_PMCSR Структура _PCI_PMCSR (wdm.h) описывает содержимое регистра состояния управления питанием устройства. |

| PCI_PMCSR_BSE Структура _PCI_PMCSR_BSE (wdm.h) описывает содержимое регистра состояния управления питанием для расширений поддержки моста PCI. |

| PCI_VENDOR_SPECIFIC_CAPABILITY Структура PCI_VENDOR_SPECIFIC_CAPABILITY… |

| PCI_VIRTUALIZATION_INTERFACE Дополнительные сведения о структуре PCI_VIRTUALIZATION_INTERFACE |

| PCI_X_CAPABILITY Структура PCI_X_CAPABILITY (wdm.h) сообщает содержимое регистров команд и состояний устройства, соответствующего надстройке PCI-X спецификации локальной шины PCI. |

fpga4fun.com — PCI 1 — Как работает PCI

Здесь мы сосредоточимся на 32-разрядной шине PCI 2.2, которая используется в современных ПК.

Более новые версии PCI включают PCI 2.3 и PCI 3.0.

Спецификация PCI

PCI разрабатывается и поддерживается группой под названием PCI Special Interest Group (сокращенно PCI-SIG).

В отличие от спецификации Ethernet, спецификацию PCI нельзя загрузить бесплатно.

Вы должны быть членом PCI-SIG, чтобы получить доступ к спецификации.

Поскольку членство обходится дорого, вы можете проверить группу оборудования вашей компании (при условии, что вы работаете в полупроводниковой промышленности), чтобы узнать, можете ли вы получить доступ к спецификации.

В противном случае вот краткое введение, за которым следуют несколько ссылок для получения дополнительной информации.

Характеристики PCI

Шина PCI имеет 4 основные характеристики:

- Синхронный

- Ориентирован на транзакции/пакеты

- Мастеринг шины

- Подключи и работай

PCI синхронный

Шина PCI использует один такт.

Тактовая частота по умолчанию работает на частоте 33 МГц, но может работать ниже (вплоть до простоя = 0 МГц) для экономии энергии или выше (66 МГц), если ваше оборудование поддерживает это.

PCI ориентирован на транзакции/пакеты

PCI ориентирован на транзакции.

- Вы начинаете транзакцию

- Вы указываете начальный адрес (один такт)

- Вы отправляете столько данных, сколько хотите (много следующих тактов)

- Вы завершаете транзакцию

PCI — это 32-битная шина, поэтому для передачи данных имеется 32 линии.

В начале транзакции шина используется для указания 32-битного адреса.

После указания адреса может пройти много циклов данных. Адрес не передается повторно, а автоматически увеличивается при каждом цикле данных.

Чтобы указать другой адрес, транзакция останавливается и начинается новая.

Таким образом, полоса пропускания PCI лучше всего используется в пакетном режиме.

PCI разрешает управление шиной

Транзакции PCI работают в отношениях ведущий-ведомый.

Мастер — это агент, который инициирует транзакцию (может быть чтение или запись).

В то время как центральный ЦП часто является мастером шины, все платы PCI потенциально могут претендовать на шину и стать мастером шины.

PCI поддерживает автоматическую настройку

Платы PCI являются plug-and-play. Это означает, что хост-ЦП/хост-ОС может:

- Определение идентификатора каждой платы PCI на шине PCI (производитель и функция (видео, сеть…))

- Определить возможности/требования каждой платы (сколько памяти требуется, сколько прерываний…)

- Переместить пространство памяти каждой платы

Последняя функция является важной частью plug-and-play.

Каждая плата отвечает на некоторые адреса, но адреса, на которые она отвечает, можно запрограммировать (т. е. каждая плата генерирует свои собственные сигналы выбора платы/чипа).

Это позволяет ОС «сопоставлять» адресное пространство каждой платы там, где она хочет.

PCI «пробелы»

PCI определяет 3 «пространства», где вы можете читать и писать.

Когда транзакция начинается, мастер указывает начальный адрес транзакции, если это чтение или запись, И с каким пространством он хочет говорить.

- Объем памяти

- Пространство ввода-вывода

- Пространство конфигурации

Они работают следующим образом:

- Пространства памяти и ввода-вывода являются рабочими местами.

Они «перемещаемые» (т. е. адреса, по которым отвечает каждая плата, могут быть перемещены). - Пространство конфигурации используется для plug-and-play.

Это пространство, в котором каждая плата должна реализовывать очень определенные регистры по очень конкретным адресам, чтобы хост-ЦП/ОС мог выяснить, каковы особенности/способности/требования каждой платы.

Оттуда центральный ЦП/ОС включает и настраивает два других пространства.

Это пространство фиксировано и всегда начинается с адреса 0 для всех плат PCI; поэтому одна линия разъема PCI используется для выбора платы (только для этого места).

Чтобы быть совместимым, плата PCI должна реализовать пространство конфигурации.

Пространства памяти и ввода-вывода необязательны, но на практике всегда используются одно или оба.

Мост PCI

Устройства PCI не подключаются напрямую к центральному процессору, а проходят через микросхему «моста».

Это связано с тем, что ЦП обычно не «говорят» на PCI изначально, поэтому мост должен переводить транзакции с шины ЦП на шину PCI.

Также процессоры никогда не имеют 3 области памяти, как устройства PCI.

Большинство ЦП имеют 1 пространство (пространство памяти), в то время как другие ЦП имеют 2 (память и ввод-вывод).

Мост должен проделать некоторые трюки, чтобы ЦП все еще мог получить доступ ко всем трем пространствам PCI.

Напряжение PCI

Платы PCI могут использовать сигнализацию 3,3 В или 5 В.

Интересно, что все современные ПК используют сигнализацию 5 В.

Разъемы платы PCI имеют один или два слота, которые определяют, совместима ли плата с напряжением 3,3 В или 5 В.

Это делается для того, чтобы, например, плата только на 3,3 В не могла быть подключена к шине PCI ПК только на 5 В.

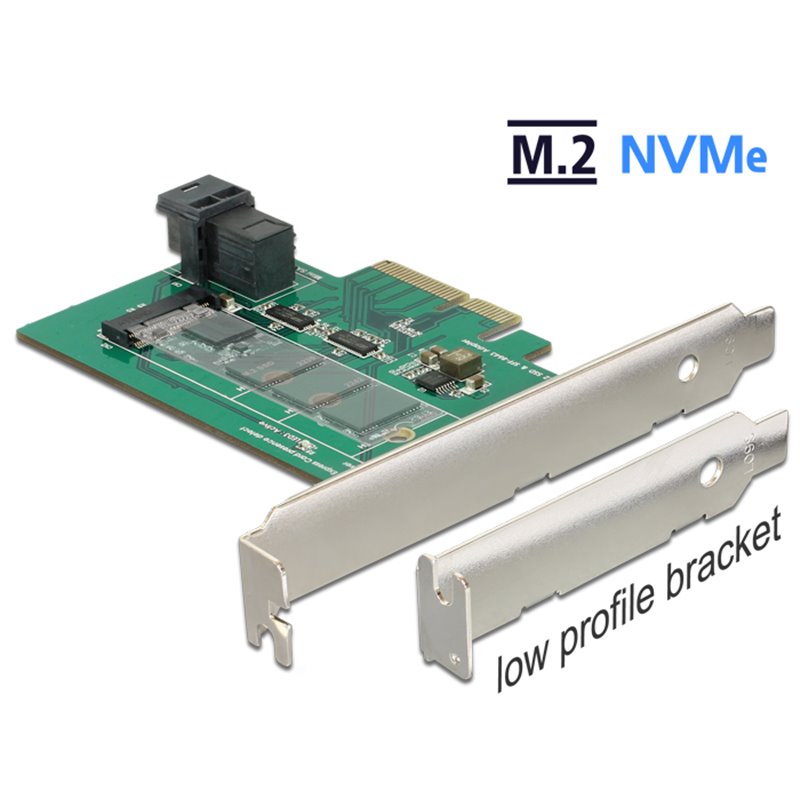

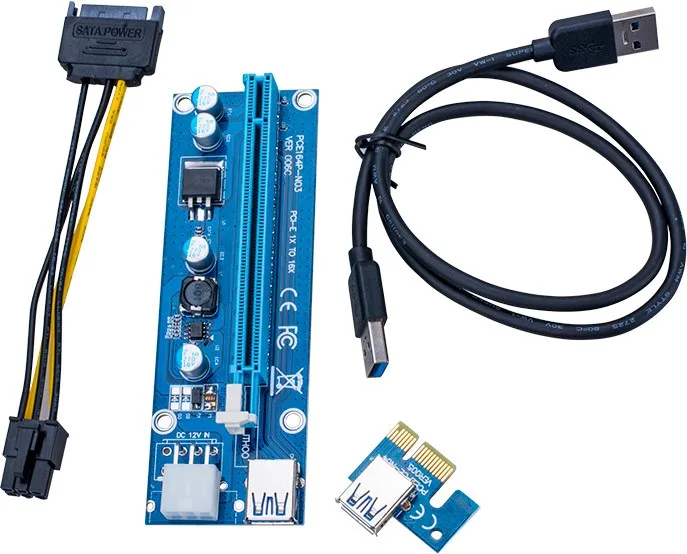

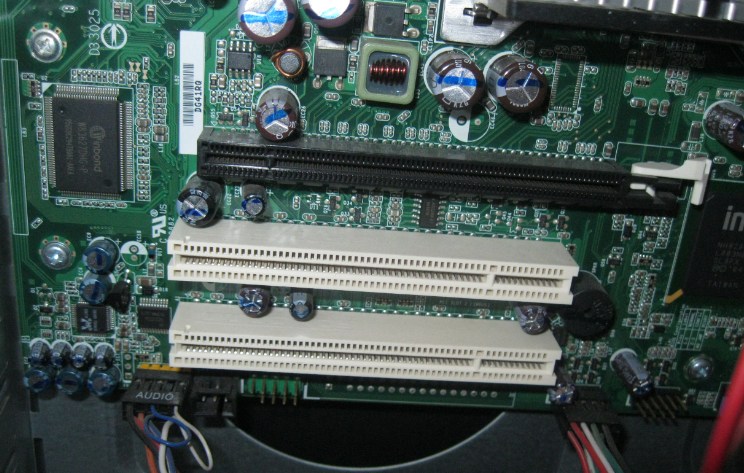

Вот пример платы только на 5 В:

, в то время как эта плата совместима как с 5 В, так и с 3,3 В:

Время PCI

PCI определяет время, связанное с его часами.

С тактовой частотой 33 МГц мы имеем:

- 7 нс/0 нс Tsu/Th (установка/удержание) ограничение на входах

- 11 нс Tco (тактовая частота-выход) на выходах

Ссылки

- Краткая страница работы шины PCI.

- Также эксперимент по созданию платы PCI

Информация о шине PCI и код

Информация о шине PCI и код

Информация о шине PCI и код с точки зрения программиста.

ноябрь 2007 г. обновлено для PCIe!

, август 2010 г. , снова обновлено для PCIe!

, снова обновлено для PCIe!

Подсистема PCI состоит из 4 компонентов:

Номер шины

Номер устройства

Номер функции

Номер регистра

В системе PCI доступно до 256 шин, чаще всего все карты и

микросхемы будут расположены на шине 0 и шине 1.

При поиске аппаратного обеспечения рекомендуется сканировать все 256 шин, так как это не займет

много дополнительного времени.

Устройство — это физическое устройство на шине PCI. Это может быть видеокарта, Ethernet

карта, северный мост, что угодно. Программное обеспечение поддерживает не более 32 устройств.

существуют на каждом автобусе. Предел физического оборудования намного ниже из-за

проблемы с электрической нагрузкой, но мы не будем об этом.

Устройства на материнской плате обычно разбросаны по 32 устройствам, отверстия могут и

будет существовать. Ваше программное обеспечение должно сканировать все 32 устройства на каждой шине.

Все устройства имеют как минимум 1 функцию, функция №0. Каждое устройство может иметь 8 возможных функций, пронумерованных от 0 до 7. Любое устройство, имеющее

Каждое устройство может иметь 8 возможных функций, пронумерованных от 0 до 7. Любое устройство, имеющее

более 1 функции (эй умно!) называется многофункциональным устройством. Многофункциональные устройства, такие как

Комбинация модем+звуковая карта обычно имеет 2 функции с уникальной адресацией, пронумерованные 0 и 1.

Каждая функция устройства имеет 256 восьмибитных регистров. Регистры 0-3F

определяется спецификацией PCI и предоставляет обширную информацию о конкретных

функция. Регистры 40-FF определяются поставщиком и управляют свойствами

сама функция. Без специальной документации поставщика эти регистры должны

скорее всего останется нетронутым.

Типичная функция PCI выглядит так:

x0 x1 x2 x3 x4 x5 x6 x7 x8 x9 xA xB xC xD xE xF 00000000: В7 10 55 90 17 01 10 02 30 00 00 02 08 50 00 00 00000010: 81 10 00 00 00 00 00 0С 00 00 00 00 00 00 00 00 00000020: 00 00 00 00 00 00 00 00 00 00 00 00 В7 10 55 90 00000030: 00 00 00 00 DC 00 00 00 00 00 00 00 0B 01 0A 0A 00000040: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00000050: 00 00 00 00 40 00 00 00 00 00 00 00 00 00 00 00 00000060: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00000070: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00000080: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00000090: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 000000A0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 000000B0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 000000C0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 000000D0: 00 00 00 00 00 00 00 00 00 00 00 00 01 00 01 F6 000000E0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 000000F0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

Регистры 0 и 1 определены спецификацией PCI как идентификатор поставщика. Продавец

Продавец

ID — это 16-битное значение, в данном случае 10B7h

Регистры 2 и 3 являются идентификатором устройства, в данном примере 9055h.

Путем поиска идентификационного номера поставщика 10b7 в базе данных поставщиков PCI

Вы можете видеть, что это карта 3COM. 9055h — это 3COM.

сгенерированное число, описывающее модель карты.

Другие регистры могут сказать нам, что это контроллер Ethernet, он использует IRQ 11, использует базу

Адрес ввода/вывода 1080h и более. Обратитесь к спецификации PCI, чтобы получить все подробности,

поскольку они выходят за рамки этого документа.

Так как же добраться до всех этих регистров в пространстве PCI?

Доступ к этим регистрам похож на доступ к памяти CMOS, поскольку сначала вы отправляете индекс .

значение (указатель на регистр, к которому вы хотите получить доступ) в индексный порт, затем вы читаете или

запишите данные в/из порта данных. Индекс будет

комбинация всех 4 вышеупомянутых компонентов (шина, устройство, функция, регистр)

В мире x86 индекс 9Порт 0171 всегда расположен по адресу 0CF8h, а данные — .

порт всегда находится по адресу 0CFCh в пространстве ввода-вывода. Большинство системных BIOS имеют программное обеспечение.

интерфейсы, чтобы абстрагировать от вас доступ к индексу/порту данных. Я описываю оба метода

ниже. Обратитесь к списку прерываний Ральфа Брауна для получения подробной информации о методе BIOS.

чтение/запись PCI

Прежде чем вы сможете получить доступ к регистрам любой функции PCI, вы, вероятно, должны убедиться, что

Интерфейс PCI существует первым!

Обнаружение шины PCI

, вы можете обнаружить шину PCI несколькими способами. проще всего позвонить

Интерфейс PCI BIOS напрямую и выполните проверку установки.

обратите внимание, что вы также можете выполнить проверку не-80386+, выполнив этот вызов и проверяя только DX для

«CP» (4350h), а вы когда-нибудь видели 286 с шиной PCI?

.386

мов топор, 0b101h ; функция прерывания 1a b101

интервал 1ah ; скажет нам, есть ли PCI

cmp edx, "ICP" ; автобус на борту. джз ага ; ЕДВ=20494350ч

джз ага ; ЕДВ=20494350ч ; Нет ага:

————————————

Вы также можете найти шину PCI с помощью ввода-вывода, просто выполнив быстрое чтение порта CFCh.

мов дх, 0cfch ; порт данных конфигурации в еах, дх см еакс, -1 ; ФФФФФФФ? джз нет ; что-то должно существовать в земле PCI

; ага

нет:

вы просто получите данные последней завершенной операции PCI.

Это ни в коем случае не надежный метод, но он может сделать работу для быстрого и грязного типа.

Приложения.

поиск устройства на шине PCI :

существует 2 способа найти устройство PCI на шине. Вы можете использовать PCI

Вызов интерфейса BIOS или прямой аппаратный ввод-вывод.

Вот путь BIOS:

INTEL_VENDOR_ID EQU 8086h ; уникальный знак Intel # INTEL_EXP_NIC EQU 1227h ; образец устройства PCI etherexpress 10/100 NIC

.386 мов топор, 0b102h ; функция прерывания 1a b102 mov dx, INTEL_VENDOR_ID mov cx, INTEL_EXP_NIC хор си, си; 0=1-е устройство, 1=2-е и т.д. интервал 1ah Джей Си нет ; после возврата из этого вызова, BH=номер шины, BL=устройство/функция #

нет:

————————————————— —————

в приведенном выше примере, SI обычно будет равен нулю, если вы не пытаетесь найти 2-й или

больше экземпляров одного и того же устройства PCI.

(т. е. у вас было установлено 3 карты PCI intel etherexpress)

Чрезвычайно удобная утилита для просмотра шины PCI в вашей системе — это DOS

программа под названием PCIVIEW.EXE. я смог найти эту утилиту в сети, просто

ищу pciview.exe

————————————————— —————————————————-

способ без BIOS:

поиск определенного устройства на шина PCI требует от вас понимания того, как

цикл настройки прерывается.

это 32-битное значение, которое выглядит так:

бит 31=1 (бит всегда установлен для доступа PCI)

бит 30:24=0 (зарезервировано)

бит 23:16=номер шины (0-255)

бит 15:11=номер устройства (0-31)

bits10:8=функция # (0-7)

bits7:0=номер регистра (0-255)

вы отправляете указанное выше значение в битовом кодировании на индексный порт (cf8h), а затем выполняете 32-битное чтение

из порта данных (cfch)

вот как прочитать поставщика и идентификатор устройства с устройства, находящегося на шине 0, устройство 7,

функция 3.

ШИНА ЭКВ 0 РАЗРАБОТКА ЭКВ 7 ФН ЭКВ 3 VEN_ID EQU 0 ; идентификатор поставщика = регистры PCI 0,1 PCI_INDEX EQU 0CF8h PCI_DATA EQU 0CFCh

.386

мов топор, 8000ч ; установить бит 31 (после сдвига)

или al, BUS ; добавить номер автобуса

шл эакс, 16 мов топор, ДЕВ

шл топор, 11 ; слайд-устройство # до бит 15:11

мов ал, ФН

или ах, ал; добавить функцию в биты 10:8

mov al, VEN_ID кли

mov dx, PCI_INDEX

вне дх, еах ; отправьте наш запрос на номер мов дх, PCI_DATA

в еах, дх ; прочитать обратно 32-битное значение.

сти

Помните, что регистры PCI представляют собой 8-битные значения. Приведенное выше чтение из PCI_DATA читает

32-битное значение или 4 регистра PCI. В приведенном выше примере после чтения EAX =

идентификатор устройства, AX = идентификатор поставщика.

В соответствии со спецификацией PCI идентификатор поставщика всегда состоит из регистров 0 и 1, а идентификатор устройства —

регистры 2 и 3.

Таким образом, AL=регистр 0, AH=регистр 1, EAL=регистр 2, EAH=регистр 3.

Обновление PCIe:

PCI Express внесла небольшие изменения в интерфейс. В частности, они изменили номер

регистров конфигурации с 256 по 4096. Первые 256 регистров выглядят так же, как

обычные регистры PCI — на самом деле они также доступны для чтения и записи с использованием тех же методов

описано выше.

Однако дополнительные регистры доступны только через подсистему с отображением памяти и

это полная боль в щеках, чтобы добраться до них. **обновление, август 2010 г., см. ниже!**

Для PCIe оказалось, что *ВСЯ* подсистема PCI была отображена на 256-мегабайтный кусок памяти.

системная память. На 2-х машинах, с которыми мне довелось поиграться, эта карта памяти запускалась

по физическому адресу 0xe0000000. Это почти 4 гига памяти. Я предлагаю

вы берете браузер/редактор памяти, который позволяет вам ковыряться в памяти и

исследовать местность самостоятельно.

В 0xe0000000 вы увидите копию каждого регистра PCI(e) с шины 0, устройства 0, функции 0.

Функция 1 следует по адресу 0xe0001000, функция 2 по адресу 0xe0002000 и т. д., вплоть до шины 255,

Устройство 31, функция 7. Каждая функция PCI, PCIe или нет, отображается на использование 0x1000 (4 КБ) пространства!

(спасибо Lihan Liang за разъяснения!)

Каждый раз, когда отсутствовало устройство PCI, такое как BUS 89, Device 9, Function 3, память просто

возвращает все FF, потому что нечего ответить на чтение. Для меня это кажется ОГРОМНЫМ

пустая трата памяти, учитывая, что уже существует отличный механизм для

доступ к PCI, и все, что им нужно сделать, это использовать пару зарезервированных битов в 32-битном

index, чтобы разрешить доступ ко всем расширенным регистрам PCIe, но я отвлекся…

Изменение любого значения регистра здесь, в памяти, точно так же, как изменение их через порты ввода-вывода по-старому; в

карта памяти — это просто зеркало того, что вы видите через порты индекса и данных, и наоборот.

На вашем компьютере ваша карта памяти PCIe может быть не на 0xe0000000. Как я нашел это волшебство

ценность? Вот где начинается боль в щеках, с ACPI.

В таблице описания корневой системы ACPI (RSDT) спрятана запись для

Базовый адрес пространства конфигурации с отображением памяти PCI Express Таблица описания или MCFG для

короткая.

Чтобы попасть туда, вам нужно проанализировать таблицы ACPI. Вот как это сделать:

1) поиск в памяти (реальный режим) в сегментах BIOS 0xE000 или 0xF000 последовательности байтов:

«RSD PTR»

1a) RSD PTR также может находиться в области EBDA (обычно между 638 и 640k).

Это явно для людей, пропатчивших таблицы, которые переместили RSDT в область оперативной памяти.

Предположительно, в первую очередь ищется область оперативной памяти, хотя это специально не оговаривается, но она стоит первой в списке. (спасибо Генри!)

2) добавить 0x10 к адресу, где найден «RSD PTR», чтобы получить 32-битный указатель на то, где находится

расположены основные таблицы ACPI RSDT.

3) Вам нужно будет находиться в защищенном режиме или в нереальном режиме, чтобы получить доступ к памяти, чтобы выполнить следующую часть.

Начиная с 32-битного адреса таблиц RSDT (должно быть в верхней памяти, мой NVidia

плата поместила их по адресу 0x7FEF3040) ищем по ключевому слову «MCFG» или просматриваем все таблицы

пока не дойдете до одного с надписью «MCFG». По смещению 0x2c от «MCFG» будет еще 32 бита

указатель на карту памяти PCIe.

Таблица «MCFG» моей платы Nvidia выглядит следующим образом:

4D434647 3C000000 012C4E76 69646961 MCFG

У меня есть программа дампа ACPI (для DOS) здесь:

http://www.waste.org/~winkles/acpidump

хотя он устарел и не выгружает таблицу MCFG, он, по крайней мере, укажет вам

в правильном направлении, куда смотреть.Мне показалось, что очень немногие устройства PCIe имеют какие-либо дополнительные регистры выше 255.

которые доступны через порты индекса и данных, поэтому доступ к ним таким образом выглядит

немного спорный вопрос, но я уверен, что в конце концов что-то придумается, так что теперь вы знаете.

h) описывает возможности устройства PCI Express (PCIe) для структуры возможностей PCIe.

h) описывает возможности устройства PCI Express (PCIe) для структуры возможностей PCIe. h) описывает заголовок расширенной структуры возможностей PCI Express (PCIe).

h) описывает заголовок расширенной структуры возможностей PCI Express (PCIe).

Не используйте.

Не используйте.

h) описывает дополнительный регистр состояния незаменяемой ошибки PCI Express (PCIe).

h) описывает дополнительный регистр состояния незаменяемой ошибки PCI Express (PCIe). h) описывает регистр незаменяемой маски ошибки PCI Express (PCIe).

h) описывает регистр незаменяемой маски ошибки PCI Express (PCIe). См. раздел 7.y.7.

См. раздел 7.y.7.

джз ага ; ЕДВ=20494350ч

джз ага ; ЕДВ=20494350ч  д.

интервал 1ah

Джей Си нет

; после возврата из этого вызова, BH=номер шины, BL=устройство/функция #

д.

интервал 1ah

Джей Си нет

; после возврата из этого вызова, BH=номер шины, BL=устройство/функция #