Шины и интерфейсы: FSB, шины расширения, внешние компьютерные шины. Pci 1 шина

PCI – шина

PCI - шина

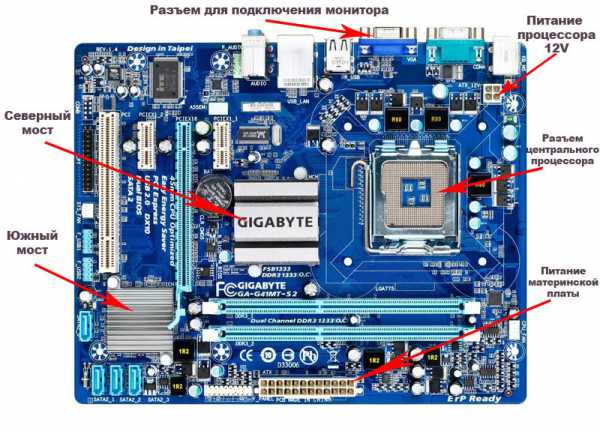

PCI (Peripheral Component Interconnect bus) - шина для подсоединения периферийных устройств. Стала массово применяться для Pentium-систем, но используется и с 486 процессорами. Частота шины от 20 до 33 МГц, теоретически максимальная скорость 132/264 Мбайт/с для 32/64 бит. В современных материнских платах частота на шине PCI задается как 1/2 входной частоты процессора, т.е при частоте 66 MHz на PCI будет 33 MHz, при 75 MHz - 37.5 MHz.

Имеет версии с питанием 5V, 3.3V и универсальную (с переключением линий +VI/O c 5V на 3,3V). Ключами являются пропущенные ряды контактов 12, 13 и 50, 51. Для слота с питанием 5V ключ расположен на месте контактов 50, 51, для 3,3 В - 12, 13, а для универсального - два ключа: 12, 13 и 50,51. 32-битный слот заканчивается контактами А62/В62, 64-битный - А94/В94.

Слот PCI самодостаточен для подключения любого контроллера на системной плате может сосуществовать с любой из других шин ввода-вывода.

Шина PCI - первая шина в архитектуре IBM PC, которая не привязана к этой архитектуре. Она является процессорно-независимой и применяется, например, в компьютерах Macintosh.

В отличие от остальных шин, компоненты расположены на левой поверхности плат PCI-адаптеров. По этой причине крайний PCI-слот обычно разделяет использование посадочного места с соседним ISA-слотом (Shared slot).

Процессор через так называемые мосты (PCI Bridge) может быть подключен к нескольким каналам PCI, обеспечивая возможность одновременной передачи данных между независимыми каналами PCI.

Автоконфигурирование устройств (выбор запросов прерывания, каналов DMA) поддерживается средствами BIOS материнской платы по образу и подобию стандарта Plug & Play.

Стандарт PCI определяет для каждого слота конфигурационное пространство размером до 256 восьмибитных регистров, не приписанных ни к пространству памяти, ни к пространству ввода-вывода. Доступ к ним осуществляется по специальным циклам шины Configuration Read и Configuration Write, вырабатываемым контроллером при обращении процессора к регистрам контроллера шины PCI, расположенным в его пространстве ввода-вывода.

На PCI определены два основных вида устройств - инициатор (по ГОСТ - задатчик), т.е. устройство, получившее от арбитра шины разрешение на захват ее и устройство назначения, цель (target) с которым инициатор выполняет цикл обмена данными.

Поддержка "горячей" замены PCI устройств, называемой в стандарте как PCI Hot-Plug. Ввод этой функции позволит добавлять/изымать PCI платы без выключения компьютера. Такая возможность особенно необходима для серверных платформ

Система управления энергопотреблением для устройств на шине PCI. Позволяет управлять энергопотреблением как для внешних PCI плат так и для встроенных на материнской плате устройств. Механизм управления подстроен под стандарт ACPI для облегчения управления энергопотреблением PCI устройств со стороны операционной системы.

Дополнены и переработаны требования к конструктивной реализации PCI плат.

Сигналы шины PCI

Знак - (минус) перед названием сигнала означает, что активный уровень этого сигнала логический ноль, обозначение {XX:0} означает группу сигналов с номерами от 0 до XX.

AD {31:0} - мультиплексированная шина адреса/данных. Адрес передается по сигналу - FRAME, в последующих тактах передаются данные.

-C/ BE {3:0} - команда/разрешение обращения к байтам. Команда, определяющая тип очередного цикла шины (чтение-запись памяти, ввода/вывода или чтение/запись конфигурации, подтверждение прерывания и другие) задается четырехбитным кодом в фазе адреса по сигналу - FRAME.

-FRAME - индикатор фазы адреса (иначе - передача данных).

-DEVSEL - выбор инициатором устройства назначения.

-IRDY - готовность инициатора к обмену данными.

-TRDY - готовность устройства назначения к обмену данными.

-STOP - запрос устройства назначения к инициатору на останов текущей транзакции.

-LOCK - используется для установки, обслуживания и освобождения захвата ресурса на PCI.

-REQ {3:0} - запрос от PCI-устройства на захват шины (для слотов 3:0).

-GNT {3 0} - разрешение мастеру на использование шины.

PAR - общий бит четности для линий AD {31:0} и C/BE {3:0}.

-ParityER - сигнал об ошибке по четности (от устройства, ее обнаружившего).

-RST - сброс всех устройств.

IDSEL - выбор устройства назначения в циклах считывания и записи конфигурации.

-SERR - системная ошибка, активизируется любым устройством PCI и вызывает емаскируемое прерывание процессора (NMI).

-REQ64 - запрос на 64-битный обмен.

-ASK64 - подтверждение 64-битного обмена.

-INTR A,B,C,D - линии запросов прерывания, направляются на доступные линии IRQ BIOS компьютера. Запрос по низкому уровню допускает разделяемое использование линий прерывания.

Clock - сигнал синхронизации на тактовой частоте шины.

Test Clock, -TSTRES, TestDO, TestDI - сигналы для тестирования адаптеров по интерфейсу JTAG (на системной плате обычно не задействованы).

TSTMSLCT - перевод в режим тестирования.

Разъем шины PCI

*12, 13 - ключ для 3,3V

**50,51 - ключ для 5V

Циклы шины

По сигналам C/BE (от C/BE3 до C/BE0) во время фазы передачи адреса определяется тип цикла передачи данных.

Подтверждение прерывания (0000)

Контроллер прерываний автоматически распознает сигнал INTA и реагирует на него передачей вектора прерывания по шине AD.

Специальный цикл (0001)

Чтение порта (0010) и запись в порт (0011)

Порты ввода/вывода на шине PCI могут быть 8 или 16-ти разрядными, хотя собственно стандарт на шину PCI позволяет иметь 32-х разрядное адресное пространство. Это вызвано тем, что на компьютерах с архитектурой Intel x86, адрес порта может иметь не более 16 разрядов. Пока и 16-ти разрядный адрес порта не может быть использован, так как карты на шине ISAC:\www\doc2html\work\bestreferat-93864-13927654724498\input\isabus.htm могут декодировать только 10 разрядов.

Адресное пространство конфигурации доступно по адресам портов 0x0CF8 (Адрес) и 0x0CFC (Данные), причем адрес должен быть записан первым.

Чтение памяти (0110) и запись в память (0111)

По шинам AD передается адрес двойным словом (четыре байта). Сигналы AD0 и AD1 декодировать не требуется. Истинность данных определяется сигналами C/BE.

Чтение конфигурации (1010) и запись конфигурационных данных (1011)

mirznanii.com

Лабораторная работа №1. Локальная шина подключения периферийных устройств PCI. Конфигурирование устройств.

1

Министерство образования Республики Беларусь

Учреждение образования «Белорусский государственный университет

информатики и радиоэлектроники»

Кафедра электронных вычислительных машин

М.А. Курмаз

ЛАБОРАТОРНЫЙ ПРАКТИКУМ

по дисциплине «Периферийные устройства ЭВМ» с разделом "Интерфейсы ЭВМ"

для студентов специальности I-4002 01 «Вычислительные машины, системы и сети» всех форм обучения

|

| 2 |

| Содержание |

|

Лабораторная работа №1. Локальная шина подключения периферийных устройств PCI. | ||

Конфигурирование устройств. ..................................................................................................... | 3 | |

1.1. | Краткие теоретические сведения................................................................................. | 3 |

1.1.1. Основные сведения о шине PCI ................................................................................. | 3 | |

1.1.2. Программный доступ к конфигурационному пространству................................... | 5 | |

1.1.3. Конфигурационное пространство устройств PCI..................................................... | 5 | |

1.2. Задание на лабораторную работу...................................................................................... | 7 | |

1.3. Порядок выполнения работы ............................................................................................ | 7 | |

1.4. Содержание отчета............................................................................................................. | 7 | |

1.5. Контрольные вопросы........................................................................................................ | 8 | |

Лабораторная работа №2. Интерфейс подключения жестких дисков ATA. Команда | ||

идентификации устройства .......................................................................................................... | 9 | |

2.1. | Краткие теоретические сведения................................................................................. | 9 |

2.1.1. Основные сведения об интерфейсе ATA/ATAPI ..................................................... | 9 | |

2.1.2. Адресация данных в интерфейсе ATA ...................................................................... | 9 | |

2.1.3. Регистры устройства ATA ........................................................................................ | 10 | |

2.1.4. Протоколы обмена данными.................................................................................... | 14 | |

2.2. Задание на лабораторную работу.................................................................................... | 16 | |

2.3. Порядок выполнения работы .......................................................................................... | 16 | |

2.4. Содержание отчета........................................................................................................... | 19 | |

2.5. Контрольные вопросы...................................................................................................... | 20 | |

Лабораторная работа №3. Планшетные сканеры изображения. Изучение двух | ||

конкурирующих технологий изготовления светочувствительного датчика. ........................ | 20 | |

3.1. Краткие теоретические сведения................................................................................... | 20 | |

3.1.1. Сканер. Конструктивное исполнение планшетного сканера................................ | 20 | |

3.1.2. Светочувствительный датчик типа CCD................................................................. | 21 | |

3.1.3. Светочувствительный датчик типа CIS................................................................... | 22 | |

3.1.4. О параметрах качества изображения....................................................................... | 22 | |

3.2. Задание на лабораторную работу.................................................................................... | 23 | |

3.3. Порядок выполнения работы .......................................................................................... | 23 | |

3.4. Содержание отчета........................................................................................................... | 23 | |

3.5. Контрольные вопросы...................................................................................................... | 23 | |

Лабораторная работа №4. Интерфейс IEEE1394 (FireWire).................................................... | 25 | |

4.1. | Краткие теоретические сведения............................................................................... | 25 |

4.1.1. Основные сведения об интерфейсе IEEE 1394....................................................... | 25 | |

4.1.2. Пакет IOMeter – профессиональный инструмент для измерения эффективности | ||

подсистемы ввода-вывода.................................................................................................. | 26 | |

4.1.3. Принцип работы пакета IOMeter ............................................................................. | 26 | |

4.2. Задание на лабораторную работу.................................................................................... | 30 | |

4.3. Порядок выполнения работы .......................................................................................... | 30 | |

4.4. Содержание отчета........................................................................................................... | 31 | |

4.5. Контрольные вопросы...................................................................................................... | 31 | |

3

Цель работы: Изучить способы адресации устройств PCI. Отработать метод опроса, идентификации и конфигурирования устройств.

1.1. Краткие теоретические сведения

1.1.1. Основные сведения о шине PCI

PCI (Peripheral Component Interconnect) – шина соединения периферийных компонентов, является основной шиной расширения современных компьютеров. Она разрабатывалась в расчете на платформу Intel Pentium, но нашла применение и на более современных платформах. Первая версия PCI 1.0 появилась в 1992 г. В настоящее время развитие шины PCI приостановлено ввиду появления периферийной шины нового поколения – PCI Express. Последней официальной версией, изданной курирующей организацией PCI SIG (Special Interest Group), является версия PCI 3.0. Это полностью переработанная спецификация шины, в которую внесены некоторые изменения, например, исключена поддержка устройств с напряжением питания 5 В.

Поначалу шина PCI вводилась как пристройка (mezzanine bus) к системам с основной шиной ISA, став позже центральной шиной: она соединяется с системной шиной процессора высокопроизводительным мостом (северным), входящим в состав чипсета системной платы. Остальные шины расширения ввода-вывода(ISA/EISA или МСА), а также локальнаяISA-подобнаяшинаX-BUSи интерфейс LPC, к которым подключаются микросхемы системной платы (ROM BIOS, контроллеры прерываний, клавиатуры, DMA, портов СОМ и LPT, НГМД и прочие «мелочи»), подключаются к шине PCI через «южный» мост. В современных системных платах с хабовой архитектурой шину PCI отодвинули на периферию, не ущемляя ее в мощности канала связи с процессором и памятью, но и не нагружая транзитным трафиком устройств других шин.

Шина является синхронной — фиксация всех сигналов выполняется по положительному перепаду (фронту) сигнала CLK. Номинальнойчастотой синхронизации считается 33 МГц; начиная с версии 2.1, допускается повышение частоты до 66 МГц при поддержке всех устройств на шине (режимPCI-66).

Номинальная разрядность шины данных — 32 бита, спецификация определяет возможность расширения разрядности до 64 бит. При частоте шины 33 МГц теоретическаяпропускная способность достигает 132 Мбайт/с для32-битнойшины и 264 Мбайт/с для64-битной;при частоте синхронизации 66 МГц – 264 и 528 соответственно. Однако эти пиковые значения достигаются лишь во время передачи пакета, аиз-запротокольных накладных расходов реальная средняя суммарная (для всех задатчиков) пропускная способность шины оказывается ниже.

С устройствами PCI процессор может взаимодействовать командами обращения к памяти (MOV и т.д.) и портамввода-вывода(IN/OUT), адресованным к областям, выделенным каждому такому устройству при конфигурировании. Устройства могут вырабатывать запросы маскируемых и немаскируемых прерываний. Понятия каналов DMA для шины PCI нет, но агент шины может сам выступать в роли задатчика, поддерживая высокопроизводительный обмен с памятью (и не только) и не занимая ресурсов центрального процессора. Таким образом, к примеру, может быть реализован обмен в режиме DMA с устройствами ATА, подключенными к контролеру PCI.

Спецификация PCI требует от устройств способности перемещать все занимаемые ресурсы в пределах доступного пространства адресации. Это позволяет обеспечивать бесконфликтное распределение ресурсов для многих устройств (функций). Для управления устройствами рекомендуется вместо портовввода-выводапо возможности

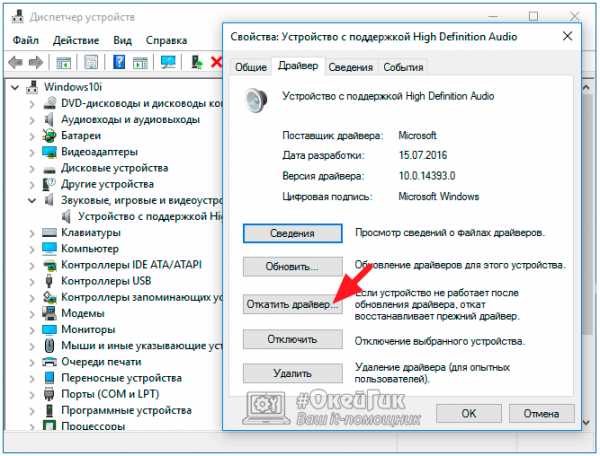

4

использовать ячейки памяти. Одно и то же функциональное устройство может быть сконфигурировано по-разному,отображая свои регистры либо на пространство памяти, либо на пространствоввода-вывода.Драйвер может определить текущую настройку, прочитав содержимое регистра базового адреса устройства. Драйвер также может определить и номер запроса прерывания, который используется устройством.

Для шины PCI принята иерархия понятий адресации: шина, устройство, функция. Эти понятия фигурируют только при обращении к регистрам конфигурационного пространства. К этим регистрам обращаются на этапе конфигурирования — переучета обнаруженных устройств, выделения им непересекающихся ресурсов (областей памяти и пространстваввода-вывода)и назначения номеров аппаратных прерываний. При дальнейшей регулярной работе устройства будут отзываться на обращения по назначенным им адресам памяти иввода-вывода,доведенным до сведения связанных с ними модулей ПО. Эти адреса принимаются с шины AD в начале каждой транзакции. Для доступа к конфигурационному пространству используются отдельные линии IDSEL.

Устройством PCI называется микросхема или карта расширения, подключенная к одной из шин PCI и использующая для идентификации выделенную ей линию IDSEL, принадлежащую этой шине. Устройство может быть многофункциональным, то есть состоять из множества (от 1 до 8) так называемыхфункций. Каждой функции отводится конфигурационное пространство в 256 байт. Многофункциональные устройства должны отзываться только на конфигурационные циклы с номерами функций, для которых имеется конфигурационное пространство. При этом функция с номером 0 должна быть обязательно, номера остальных функций назначаются разработчиком устройства произвольно (в диапазоне1-7).Простые (однофункциональные) устройства, в зависимости от реализации, могут отзываться либо на любой номер функции, либо только на номер функции 0.

Шина PCI – набор сигнальных линий, непосредственно соединяющих интерфейсные выводы группы устройств (слотов, микросхем на системной плате). В системе может присутствовать несколько шин PCI, соединенных мостами PCI. Мосты электрически отделяют интерфейсные сигналы одной шины от другой, соединяя их логически; главный мост соединяет главную шину с ядром системы (процессором и памятью). Каждая шина имеет свойномер шины (PCI bus number). Шины нумеруются последовательно; главная шина имеет нулевой номер.

С точки зрения конфигурирования, минимальной адресуемой единицей этой иерархии является функция; ее полный адрес состоит из трех частей: номера шины, номера устройства и номера функции. Короткая форма идентификации вида РСI 0:1:2 (например, в сообщениях ОС Unix) означает функцию 2 устройства 1, подключенного к главной (0) шине PCI.

В шине PCI принята географическая адресация — номер устройства определяется местом его подключения. Номер устройства (device number или dev) определяется той линией шины AD, к которой подключена линия сигнала IDSEL данного слота. Часто для слотов используются убывающие номера устройств, начиная с 20. Группы соседних слотов могут подключаться к разным шинам; на каждой шине PCI нумерация устройств независимая (могут быть и устройства с совпадающими номерами dev, но разными номерами шин). Устройства PCI, интегрированные в системную плату, используют ту же систему адресации. Их номера «запаяны намертво», в то время как адреса карт расширения можно изменять перестановкой их в разные слоты. Одна карта PCI может содержать только одно устройство шины, к которой она подключается, поскольку ей в слоте выделяется только одна линия IDSEL. Если на карте размещают несколько устройств (например,4-портоваякарта Ethernet), то на ней приходится устанавливать мост

– тоже устройство PCI, к которому и обращаются по линии IDSEL, выделенной данной карте. Этот мост организует на карте дополнительную шину PCI, к которой можно подключить множество устройств.

5

1.1.2. Программный доступ к конфигурационному пространству

Поскольку конфигурационное пространство PCI обособлено, в главный мост приходится вводить специальный механизм доступа к нему командами процессора, который «умеет» обращаться только к памяти иливводу-выводу.Этот же механизм используется и для генерации специальных циклов. ДляPC-совместимыхкомпью¬еров предусмотрено два механизма, из которых в спецификации PCI, начиная с версии 2.2, оставлен только первый (Configuration Mechanism #1). Номер механизма, которым пользуется конкретная системная плата, можно узнать путем вызова PCI BIOS.

Конфигурационные циклы адресуются к конкретному устройству (микросхеме PCI), для которого должен быть сформирован сигнал выборки IDSEL (единичное значение). Номер функции и адрес регистра декодируется самим устройством. Поскольку сигнал IDSEL воспринимается устройством только в фазе адреса, для него используют позиционное кодирование в линиях старших битов шины AD (конфигурационное пространство всех устройств занимает лишь малую часть пространства с32-битнойадресацией). На этих линиях в фазе адреса конфигурационного обращения может быть лишь один единичный бит, остальные — нулевые. Таким образом, только одно устройство будет выбрано сигналом IDSEL.

Для работы механизма № 1 в пространстве ввода-выводазарезервированы32-битныепорты с адресами 0x0CF8 и 0x0CFC, входящие в состав главного моста. Для обращения к конфигурационному пространству в порт CONFIG_ADDRESS (RW, адрес 0x0CF8) заносят32-разрядныйадрес, декодируемый в соответствии с табл. 1.1. После занесения адреса обращением к порту CONFIG_DATA (RW, адрес 0x0CFC) можно прочитать или записать содержимое требуемого конфигурационного регистра.

31 | 30 | 24 | 23 | 16 | 15 | 11 | 10 | 8 | 7 | 2 | 1 | 0 |

1 | 0000000 | номер |

|

| номер | номер |

|

| адрес | 0 | 0 | |

|

|

| шины |

| устройства | функции |

|

| регистра |

|

| |

Таблица 1.1. Формат адреса для вызова конфигурационного цикла (механизм №1)

Если конфигурационный цикл не воспринимается ни одним из устройств, мосты могут эту ситуацию отрабатывать двояко: фиксировать отсутствие устройства (сработает Master Abort) или же выполнять операции вхолостую. Однако в любом случае чтение конфигурационного регистра несуществующего устройства (функции) должно возвращать значение 0x0FFFFFFFF (это будет безопасной информацией, поскольку даст недопустимое значение идентификатора устройства). Если главный мост подключает несколько равноранговых шин (peer buses), то одна из них назначается условно главной, так что вышеописанная логика сохраняется.

1.1.3. Конфигурационное пространство устройств PCI

В стандарт PCI заложены возможности автоматического конфигурирования системных ресурсов (пространств памяти и ввода-выводаи линий запроса прерываний). Автоматическое конфигурирование устройств (выбор адресов и прерываний) поддерживается средствами BIOS и ориентировано на технологию PnP.

Стандарт PCI определяет для каждого слота конфигурационное пространство размером до 256 регистров(8-битных),не приписанных ни к пространству памяти, ни к пространствуввода-вывода.Доступ к ним осуществляется по специальным циклам шины

Configuration Read и Configuration Write, вырабатываемым с помощью одного из вышеописанных механизмов. В этом пространстве есть области, обязательные для всех устройств, и специфические. Конкретное устройство может иметь регистры не во всех адресах, но должно поддерживать нормальное завершение для адресуемых к ним

6

операций. При этом чтение несуществующих регистров должно возвращать нули, а запись выполняться как холостая операция.

После аппаратного сброса (или при включении питания) устройства PCI не отвечают на обращения к пространству памяти и ввода-вывода,они доступны только для операций конфигурационного считывания и записи. В этих операциях устройства выбираются по индивидуальным сигналам IDSEL и сообщают о потребностях в ресурсах и возможных вариантах конфигурирования. После распределения ресурсов, выполняемого программой конфигурирования (во время теста POST), в конфигурационные регистры устройства записываются параметры конфигурирования. Только после этого к устройствам становится возможным доступ по командам обращения к памяти и портамввода-вывода.Для того чтобы всегда можно было найти работоспособную конфигурацию, все ресурсы, занимаемые картами, должны быть перемещаемыми в своих пространствах. Для многофункциональных карт каждая функция должна иметь собственное конфигурационное пространство.

Конфигурационное пространство устройства начинается со стандартного заголовка, в

котором содержатся идентификаторы производителя, устройстваи его класса, а также описание требуемых и занимаемых системных ресурсов. После заголовка могут располагаться регистры, специфичные для устройства; они могут занимать адреса конфигурационного пространства в пределах 40-FFh.

Формат заголовка приведен в табл. 1.2.

смещение | 31 | 24 | 23 | 16 | 15 | 8 | 7 | 0 |

0x00 |

| Device ID |

| Vendor ID |

| |||

0x04 |

| Status |

| Command |

| |||

0x08 |

|

| Class ID |

|

|

| Revision ID |

|

0x0C |

| BIST | Header type |

| Latency timer |

| Cache line size |

|

0x10-0x24 |

|

| Base address | registers |

|

|

| |

0x28 |

|

| Cardbus CIS pointer |

|

|

| ||

0x2C |

| Subsystem ID |

| Subsystem vendor ID |

| |||

0x30 |

|

| Expansion ROM base address |

|

|

| ||

0x34 |

|

| reserve |

|

|

| Capabilities ptr |

|

0x38 |

|

|

| reserve |

|

|

| |

0x3C |

| max_lat | min_gnt |

| Interrupt pin |

| Interrupt line |

|

Таблица 1.2. Конфигурационное пространство устройства PCI, обязательные поля

Перечисленные ниже поля идентификации допускают только чтение.

•Device ID – идентификатор устройства, назначаемый производителем.

•Vendor ID – идентификатор производителя микросхемы PCI, назначенный PCI SIG. Идентификатор 0xFFFF является недопустимым; это значение должно возвращаться при чтении конфигурационного пространства несуществующего устройства.

•Revision ID – версия продукта, назначенная производителем. Используется как расширение поля Device ID.

•Header Type – тип заголовка (биты 6:0), определяющий формат ячеек в диапазоне 0x10-0x3Fи несущий признак многофункционального устройства (если бит 7=1). На рисунке приведен формат заголовка типа 0, относящийся именно к устройствам PCI. Тип 01 относится к мостамPCI-PCI;тип 02 относится к мостам шины CardBus.

•Class Code — код класса, определяющий основную функцию устройства, а иногда и его программный интерфейс. Старший байт (адрес 0x0B) определяет базовый класс, средний — подкласс, младший — программный интерфейс (если он стандартизован).

studfiles.net

Шина pci

PCI (Peripheral Component Interconnect) local bus — шина соединения периферийных компонентов является основной шиной расширения современных компьютеров. Она разрабатывалась в расчете на Pentium, но хорошо сочеталась и с процессорами 486. Сейчас PCI является четко стандартизованной высокопроизводительной и надежной шиной расширения.

Шина является синхронной — фиксация всех сигналов выполняется по положительному перепаду (фронту) сигнала CLK. Номинальной частотой синхронизации считается 33 МГц. Начиная с версии 2.1 допускается повышение частоты до 66 МГц при согласии всех устройств на шине.

Номинальная разрядность шины данных — 32 бита, спецификация определяет и расширение разрядности до 64 бит. При частоте шины 33 МГц теоретическая пропускная способность достигает 132 Мбайт/с для 32-битной шины и 264 Мбайт/с для 64-битной; при частоте синхронизации 66 МГц — 264 и 528 соответственно. Однако эти пиковые значения достигаются лишь во время передачи пакета, а из-за протокольных накладных расходов реальная средняя суммарная.

С устройствами PCI процессор может взаимодействовать командами обращения к памяти и портам ввода-вывода, адресованным к областям, выделенным каждому такому устройству при конфигурировании. Устройства могут вырабатывать запросы маскируемых и немаскируемых прерываний. Понятия каналов DMA для шины PCI нет, но агент шины может сам выступать в роли задатчика, поддерживая высокопроизводительный обмен с памятью (и не только), не занимая ресурсов центрального процессора. Таким образом, к примеру, может быть реализован обмен в режиме DMA с устройствами ATА, подключенными к контролеру PCI IDE. Спецификация PCI требует от устройств способности перемещать все занимаемые ресурсы в пределах доступного пространства адресации. Это позволяет обеспечивать бесконфликтное распределение ресурсов для многих устройств (функций). Для управления устройствами рекомендуется вместо портов ввода-вывода по возможности использовать ячейки памяти. Одно и то же функциональное устройство может быть сконфигурировано по-разному, отображая свои регистры либо на пространство памяти, либо на пространство ввода-вывода. Драйвер может определить текущую настройку, прочитав содержимое регистра базового адреса устройства. Драйвер также может определить и номер запроса прерывания, который используется устройством.

Адресация устройств pci

Для шины PCI принята иерархия понятий адресации: шина, устройство, функция. Эти понятия фигурируют только при обращении к регистрам конфигурационного пространства. К этим регистрам обращаются на этапе конфигурирования — переучета обнаруженных устройств, выделения им непересекающихся ресурсов (областей памяти и пространства ввода-вывода) и назначения номеров аппаратных прерываний. При дальнейшей регулярной работе устройства будут отзываться на обращения по назначенным им адресам памяти и ввода-вывода, доведенным до сведения связанных с ними модулей ПО (драйверов). Эти адреса принимаются с шины AD в начале каждой транзакции. Для доступа к конфигурационному пространству используются отдельные линии IDSEL

Устройством PCI называется микросхема или карта расширения, подключенная к одной из шин PCI и использующая для идентификации выделенную ей линию IDSEL, принадлежащую этой шине. Устройство может быть многофункциональным, то есть состоять из множества (от 1 до 8) так называемых функций. Каждой функции отводится конфигурационное пространство в 256 байт. Многофункциональные устройства должны отзываться только на конфигурационные циклы с номерами функций, для которых имеется конфигурационное пространство. При этом функция с номером 0 должна быть обязательно, номера остальных функций назначаются разработчиком устройства произвольно (в диапазоне 1-7). Простые (однофункциональные) устройства, в зависимости от реализации, могут отзываться либо на любой номер функции, либо только на номер функции 0.

Шина PCI — набор сигнальных линий, непосредственно соединяющих интерфейсные выводы группы устройств (слотов, микросхем на системной плате). В системе может присутствовать несколько шин PCI, соединенных мостами PCI. Мосты электрически отделяют интерфейсные сигналы одной шины от другой, соединяя их логически; главный мост соединяет главную шину с ядром системы (процессором и памятью). Каждая шина имеет свой номер шины (PCI bus number). Шины нумеруются последовательно; главная шина имеет нулевой номер.

С точки зрения конфигурирования, минимальной адресуемой единицей этой иерархии является функция; ее полный адрес состоит из трех частей: номера шины, номера устройства и номера функции. Короткая форма идентификации вида РCI 0:1:2 (например, в сообщениях ОС Unix) означает функцию 2 устройства 1, подключенного к главной (0) шине PCI.

В шине PCI принята географическая адресация — номер устройства определяется местом его подключения. Номер устройства (device number или dev) определяется той линией шины AD, к которой подключена линия сигнала IDSEL данного слота. В соседних слотах PCI, как правило, задействуются соседние номера устройств; их нумерация определяется разработчиком системной. Часто для слотов используются убывающие номера устройств, начиная с 20. Группы соседних слотов могут подключаться к разным шинам; на каждой шине PCI нумерация устройств независимая (могут быть и устройства с совпадающими номерами dev, но разными номерами шин). Устройства PCI, интегрированные в системную плату, используют ту же систему адресации. Их номера «запаяны намертво», в то время как адреса карт расширения можно изменять перестановкой их в разные слоты. Одна карта PCI может содержать только одно устройство шины, к которой она подключается, поскольку ей в слоте выделяется только одна линия IDSEL Если на карте размещают несколько устройств (например, 4-портовая карта Ethernet), то на ней приходится устанавливать мост — тоже устройство PCI, к которому и обращаются по линии IDSEL, выделенной данной карте. Этот мост организует на карте дополнительную шину PCI, к которой можно подключить множество устройств.

Номер устройства определяет номер линии запроса прерывания, которой может пользоваться устройство. Разобраться с нумерацией устройств и полученных ими линий прерываний на конкретной плате можно просто: устанавливать одну карту PCI поочередно в каждый из слотов (отключая питание) и смотреть на сообщения об обнаруженных устройствах PCI, выводимых на дисплей в конце теста POST. В этих сообщениях будут фигурировать и устройства PCI, установленные непосредственно на системной плате (и не отключенные параметрами CMOS Setup).

Заметим, что операционные системы типа Windows не довольствуются полученными назначениями номеров прерывании и изменяют их по своему усмотрению.

studfiles.net

6.2. Шина PCI

♦MEMR# (MRDC#) — чтение памяти в любой области до 16 Мбайт.

♦OWS# (SRDY#, NOWS#, ENDXFR) — укорочение текущего цикла по инициативе адресованного устройства.

♦MASTER* (MASTER 16#) — запрос от устройства, использующего 16-битныйканал DMA на управление шиной. При получении подтверждения DACK [5:7]Bus-Masterможет захватить шину.

В шине EISA на дополнительных контактах слотов (недоступных картам ISA) располагается расширение шин данных и адреса до 32 бит, а также набор сигналов, обеспечивающих передачу данных в синхронном режиме с возможностью пакетных циклов.

PCI (Peripheral Component Interconnect) local bus — шина соединения периферийных компонентов является основной шиной расширения современных компьютеров. Она разрабатывалась в расчете на Pentium, но хорошо сочеталась и с процессорами 486. Сейчас PCI является четко стандартизованной высокопроизводительной и надежной шиной расширения. Первая версия PCI 1.0 появилась в 1992 г. В PCI 2.0 (1993 г.) введена спецификация коннекторов и карт расширения. В версии 2.1 (1995 г.) введена частота 66 МГц. В настоящее время действует спецификация PCI 2.2 (декабрь 1998 г.), которая уточняет и разъясняет некоторые положения предшествующей версии 2.1. Данное описание основано на тексте стандарта «PCI Local Bus Specification. Revision 2.2» от 17.12.1998, опубликованного организацией PCI SIG (Special Interest Group).

Поначалу шина PCI вводилась как пристройка (mezzanine bus) к системам с основной шиной ISA, став позже центральной шиной: она соединяется с системной шиной процессора высокопроизводительным мостом («северным»), входящим в состав чипсета системной платы. Остальные шины расширения ввода-вывода(ISA/EISA или МСА), а также локальнаяISA-подобнаяшинаX-BUSи интерфейс LPC, к которым подключаются микросхемы системной платы (ROM BIOS, контроллеры прерываний, клавиатуры, DMA, портов СОМ и LPT, НГМД и прочие «мелочи»), подключаются к шине PCI через «южный» мост. В современных системных платах с хабовой архитектурой шину PCI Отодвинули на периферию, не ущемляя ее в мощности канала связи с процессором и памятью, но и не нагружая транзитным трафиком устройств других шин.

Шина является синхронной — фиксация всех сигналов выполняется по положительному перепаду (срронту) сигнала CLK. Номинальной частотой синхронизации считается 33 МГц, при необходимости частота может быть понижена (на машинах с процессором 486 использовали частоты 20-33МГц). Во многих случаях частоту успешно разгоняют и до 41,5 МГц (половина типовой частоты системной шины 83 МГц). Начиная с версии 2.1 допускается повышение частоты до 66 МГц при согласии всех устройств на шине. Номинальная разрядность шины данных — 32 бита, спецификация определяет и расширение разрядности до 64 бит. При частоте шины 33 МГц теоретическая пропускная способность достигает 132 Мбайт/с для32-битнойшины и 264 Мбайт/с для64-битной;при частоте синхронизации 66 МГц — 264 и 528 соответственно. Однако эти пиковые значения достигаются лишь во время передачи пакета, аиз-запротокольных накладных расходов реальная средняя суммарная .(для всехзадат-чиков)пропускная способность шины оказывается ниже.

С устройствами PCI процессор может взаимодействовать командами обращения к памяти и портам ввода-вывода,адресованным к областям, выделенным каждому такому устройству при конфигурировании. Устройства могут вырабатывать запросы маскируемых и немаскируемых прерываний. Понятия каналов DMA для шины PCI нет, но агент шины может сам выступать в роли зада'тчика, поддерживая высокопроизводительный обмен с памятью (и не только), не занимая ресурсов

центрального процессора. Таким образом, к примеру, может быть реализован обмен в режиме DMA с устройствами AT А, подключенными к контролеру PCI IDE (см. п. 9.2.1). Спецификация PCI требует от устройств способности перемещать все занимаемые ресурсы в пределах доступного пространства адресации. Это позволяет обеспечивать бесконфликтное распределение ресурсов для многих устройств (функций). Для управления устройствами рекомендуется вместо портов ввода-выводапо возможности использовать ячейки памяти. Одно и то же функциональное устройство может быть сконфигурированопо-разному,отображая свои регистры либо на пространство памяти, либо на пространствоввода-вывода.Драйвер может определить текущую настройку, прочитав содержимое регистра базового адреса устройства, — признаком пространстваввода-выводабудет единичное значение бита 0 (см. п. 6.2.12). Драйвер также может определить и номер запроса прерывания, который используется устройством.

6.2.1. Адресация устройств PCI

Для шины PCI принята иерархия понятий адресации: шина, устройство, функция. Эти понятия фигурируют только при обращении к регистрам конфигурационного пространства (см. п. 6.2.12). К этим регистрам обращаются на этапе конфигурирования — переучета обнаруженных устройств, выделения им непересекающихся ресурсов (областей памяти и пространства ввода-вывода)и назначения номеров аппаратных прерываний. При дальнейшей регулярной работе устройства будут отзываться на обращения по назначенным им адресам памяти иввода-вывода,доведенным до сведения связанных с ними модулей ПО. Эти адреса принимаются с шины AD в начале каждой транзакции. Для доступа к конфигурационному пространству используются отдельные линии IDSEL Устройством PCI называется микросхема или карта расширения, подключенная к одной из шин PCI и использующая для идентификации выделенную ей линию IDSEL, принадлежащую этой шине. Устройство может быть многофункциональным, то есть состоять из множества (от 1 до 8) так называемых функций. Каждой функции отводится конфигурационное пространство в 256 байт (см. п. 6.2.12). Многофункциональные устройства должны отзываться только на конфигурационные циклы с номерами функций, для которых имеется конфигурационное пространство. При этом функция с номером 0 должна быть обязательно, номера остальных функций назначаются разработчиком устройства произвольно (в диапазоне1-7).Простые (однофункциональные) устройства, в зависимости от реализации, могут отзываться либо на любой номер функции, либо только на номер функции 0.

Шина PCI — набор сигнальных линий (см. п. 6.2.2), непосредственно соединяющих интерфейсные выводы группы устройств (слотов, микросхем на системной плате). В системе может присутствовать несколько шин PCI, соединенных мостами PCI (см. п. 6,2.10). Мосты электрически отделяют интерфейсные сигналы одной шины от другой, соединяя их логически; главный мост соединяет главную шину с ядром системы (процессором и памятью). Каждая шина имеет свой номер шины (PCI bus number). Шины нумеруются последовательно; главная шина имеет нулевой номер.

С точки зрения конфигурирования, минимальной адресуемой единицей этой иерархии является функция; ее полный адрес состоит из трех частей: номера шины, номера устройства и номера функции. Короткая форма идентификации вида РСЮ:1:2 (например, в сообщениях ОС Unix) означает функцию 2 устройства 1, подключенного к главной (0) шине PCI.

В шине PCI принята географическая адресация — номер устройства определяется местом его подключения. Номер устройства (device number или dev) определяется той линией шины AD, к которой подключена линия сигнала IDSEL данного слота: kADU - devO(MOCT),AD12-devl,...AD31-dev20.В соседних слотах PCI, как правило,

задействуются соседние номера устройств; их нумерация определяется разработчиком системной платы (или пассивной кросс-платыв промышленных компьютерах). Часто для

слотов используются убывающие номера устройств, начиная с 20. Группы соседних слотов могут подключаться к разным шинам; на каждой шине PCI нумерация устройств независимая (могут быть и устройства с совпадающими номерами dev, но разными номерами шин). Устройства PCI, интегрированные в системную плату, используют ту же систему адресации. Их номера «запаяны намертво», в то время как адреса карт расширения можно изменять перестановкой их в разные слоты. Одна карта PCI может содержать только одно устройство шины, к которой она подключается, поскольку ей в слоте выделяется только одна линия IDSEL Если на карте размещают несколько устройств (например, 4-портоваякарта Ethernet), то на ней приходится устанавливать мост

— тоже устройство PCI, к которому и обращаются по линии IDSEL, выделенной данной карте. Этот мост организует на карте дополнительную шину PCI, к которой можно подключить множество устройств.

С точки зрения обращения к пространствам памяти и ввода-вывода,географический адрес (номер шины и устройства) безразличен (не принимая во внимание разницу в производительности, связанную с подключением устройств к разным шинам PCI). Однако номер устройства определяет номер линии запроса прерывания, которой может пользоваться устройство. Подробнее об этом см. в п. 6.2.6, здесь же отметим, что на одной шине устройства с номерами, отличающимися друг от друга на 4, будут использовать одну и ту же линию прерывания. Возможность развести их по разным линиям прерывания может появиться лишь, если они находятся на разных шинах (это зависит от системной платы).

Разобраться с нумерацией устройств и полученных ими линий прерываний на конкретной плате можно просто: устанавливать одну карту PCI поочередно в каждый из слотов (отключая питание) и смотреть на сообщения об обнаруженных устройствах PCI, выводимых на дисплей в конце теста POST. В этих сообщениях будут фигурировать и устройства PCI, установленные непосредственно на системной плате (и не отключенные параметрами CMOS Setup).

Но чтобы не было иллюзий простоты и прозрачности, отметим, что «особо умные» операционные системы (Windows) не довольствуются полученными назначениями номеров прерывании и изменяют их по своему усмотрению (что никак не может отразиться на разделяемости линий).

6.2.2. Протокол шины PCI

В каждой транзакции (обмене по шине) участвуют два устройства — инициатор (initiator) обмена, он же ведущее (master) устройство, и целевое (target) устройство (ЦУ), оно жеведомое (slave). Шина PCI все транзакции трактует как пакетные: каждая транзакция начинается фазой адреса, за которой может следовать одна или несколько фаз данных. Состав и назначение интерфейсных сигналов шины приведены в табл. 6.11.

Таблица 6.11. Сигналы шины PCI |

| |

Сигнал | Назначение |

|

AD[31:0] | Address/Data — мультиплексированная шина адреса/данных. В начале транзакции передается адрес, в | |

| последующихтактах—данные |

|

С/ВЕ[3:0]# | Command/Byte Enable — команда/разрешение обращения к байтам. Команда, определяющаятипочередного | |

| циклашины, задаетсячетырехбитнымкодомв фазе адреса | „ |

FRAME* | Кадр. Введением сигнала отмечается начало транзакции (фаза адреса), снятие сигналауказываетнато, что | |

| последующийциклпередачиданныхявляетсяпоследнимвтранзакции | |

DEVSEL* | Device Select — устройство выбрано (ответ ЦУ на адресованную к нему транзакцию) | |

IRDY* | Initiator Ready — готовность ведущего устройства к обмену данными | |

TRDY* | Target Ready — готовность ЦУ к обмену данными |

|

STOP* | ЗапросЦУкведущемуустройствунаостановкутекущейтранзакции | |

LOCK* | Сигнал захвата шины для обеспечения целостного выполнения операции. Используетсямостом, которомудля | |

| выполненияоднойоперациитребуетсявыполнить несколько транзакций PCI | |

REQ# | Request — запрос от ведущего устройства на захват шины |

|

GNT# | Grant — предоставление ведущему устройству управления шиной | |

PAR | Parity — общий бит паритета для линий AD[31:0] и С/ВЕ[3:0]# | |

PERR* | Parity Error — сигнал об ошибке паритета (для всех циклов, кроме специальных). Вырабатывается любым |

| устройством, обнаружившимошибку |

РМЕ# | Power Management Event — сигнал о событиях, вызывающих изменение режима |

| потребления (дополнительный сигнал, введенный в PCI 2.2) |

CLKRUN* | Clock running — шина работает на номинальной частоте синхронизации. Снятие сигналаозначает |

| замедлениеилиостановкусинхронизациисцельюсниженияпотребления(длямобильныхприменений) |

PRSNT[1,2]# Present — индикаторы присутствия платы, кодирующие запрос потребляемой мощности. Накарте расширенияоднаилидвелиниииндикаторовсоединяютсяс шиной GND, что воспринимается системной платой

RST# | Reset — сброс всех регистров в начальное состояние |

IDSEL | Initialization Device Select — выбор устройства в циклах конфигурационного |

| считыванияизаписи |

SERR# | System Error — системная ошибка. Ошибка паритета адреса данных в специальном циклеилииная |

| катастрофическаяошибка, обнаруженнаяустройством. Активизируется любым устройством PCI и вызывает |

| NMI |

REQ64* | Request 64 bit — запрос на 64-битныйобмен. Сигнал вводится64-битным |

| инициатором, по времени он совпадает с сигналом FRAME*. Во время окончания сброса (сигналом |

| RST*) сигнализирует 64-битномуустройству о том, что оноподключенок64-битнойшине.Если64-б.итное |

| устройствонеобнаружитэтогосигнала, онодолжнопереконфигурироватьсяна32-битныйрежим,отключив |

| буферныесхемыстаршихбайтов |

АСК64* | Подтверждение64-битногообмена.Сигналвводится64-битнымЦУ,опознавшимсвой адрес, одновременно с |

| DEVSEL*. Отсутствие этого подтверждения заставитинициаторвыполнятьобменс32-битнойразрядностью |

INTA#, INTB*, Interrupt А, В, С, D — линии запросов прерывания, чувствительность к уровню, INTC#, INTD* активный уровень — низкий, что допускает разделяемость (совместное использование)линий

CLK | Clock — тактовая частота шины. Должна лежать в пределах 20—33МГц, |

| вPCI2.1— до 66 МГц |

M66EN | 66MHz Enable — разрешение частоты синхронизации до 66 МГц |

Сигнал | Назначение |

|

SDONE | Snoop Done — сигнал завершенности цикла слежения для текущей транзакции. Низкийуровеньуказываетна | |

| незавершенностьцикласлежениязакогерентностьюпамятиикэша. Необязательныйсигнал, используетсятолько | |

| устройствамишиныскэшируемойпамятью | |

SBO# | Snoop Backoff — попадание текущего обращения к памяти абонента шины | |

| вмодифицированнуюстрокукэша. Необязательныйсигнал, используетсятолькоабонентамишиныскэшируемой | |

| памятьюприалгоритмеобратнойзаписи | |

ТСК | Test Clock — синхронизация тестового интерфейса JTAG | |

TDI | Test Data Input — входные данные тестового интерфейса JTAG | |

TOO | Test Data Output — выходные данные тестового интерфейса JTAG | |

TMS | Test Mode Select — выбор режима для тестового интерфейса JTAG | |

TRST | Test Logic Reset — сброс тестовой логики | |

В каждый момент времени шиной может управлять только одно ведущее устройство, получившее на это право от арбитра. Каждое ведущее устройство имеет пару сигналов — REQ# для запроса на управление шиной и GNT* для подтверждения предоставления управления шиной. Устройство может начинать транзакцию (устанавливать сигнал FRAME*) только при активном полученном сигнале GNT*. Снятие сигнала GNT* не позволяет устройству начать следующую транзакцию, а при определенных условиях (см. ниже) заставляет прекратить начатую транзакцию. Арбитражем запросов на использование шины занимается специальный узел, входящий в чипсет системной платы. Схема приоритетов (фиксированный, циклический, комбинированный) определяется программированием арбитра.

Для адреса и данных используются общие мультиплексированные линии AD. Четыре мультиплексированные линии С/ВЕ[3:0] обеспечивают кодирование команд в фазе адреса и разрешения байт в фазе данных. В начале транзакции ведущее устройство активизирует сигнал FRAME*, по шине AD передает целевой адрес, а по линиям С/ВЕ# — информацию

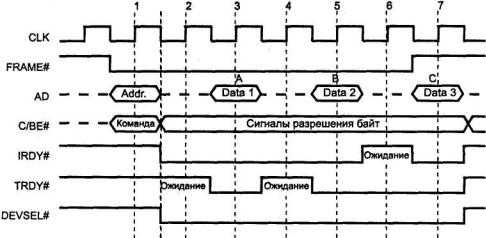

о типе транзакции (команде). Адресованное ЦУ отзывается сигналом DEVSEL*. Ведущее устройство указывает на свою готовность к обмену данными сигналом IRDY#, эта готовность может быть выставлена и раньше получения DEVSEL*. Когда к обмену данными будет готово и ЦУ, оно установит сигнал TRDY*. Данные по шине AD передаются только при одновременном наличии сигналов IRDY# и TRDY*. С помощью этих сигналов ведущее устройство и ЦУ согласуют свои скорости, вводя такты ожидания. На рис. 6.7 приведена временная диаграмма обмена, в которой и ведущее устройство, и ЦУ вводят такты ожидания. Если бы они оба ввели сигналы готовности в конце фазы адреса и не снимали их до конца обмена, то в каждом такте после фазы адреса передавались бы по 32 бита данных, что обеспечило бы выход на предельную производительность обмена.

Количество фаз данных в пакете явно не указывается, но перед последней фазой данных ведущее устройство при введенном сигнале IRDY* снимает сигнал FRAME*. В одиночных транзакциях сигнал FRAME* активен лишь один такт. Если устройство не поддерживает пакетные транзакции в ведомом режиме, то оно должно потребовать прекращения пакетной транзакции во время первой фазы данных (введя сигнал STOP* одновременно с TRDY*). В ответ на это ведущее устройство завершит данную транзакцию и продолжит обмен последующей транзакцией с новым значением адреса. После последней фазы данных ведущее устройство снимает сигнал IRDY#, и шина переходит в состояние покоя (PCI Idle) — оба сигнала FRAME* и IRDY# находятся в пассивном состоянии. Инициатор может начать следующую транзакцию и без такта покоя, введя FRAME* одновременно со снятием IRDY#. Такие быстрые смежные транзакции (Fast Back-to-Back)могут быть обращены как к одному, так и к разным ЦУ. Первый тип поддерживается всеми устройствами PCI, выступающими в роли ЦУ. На поддержку второго типа (она необязательна) указывает бит 7 регистра состояния (см. п. 6.2.12). Инициатору разрешают (если он умеет) использовать быстрые смежные транзакции с разными устройствами (битом 9 регистра команд), только если все агенты шины допускают быстрые обращения.

Рис. 6.7. Цикл обмена на шине PCI

Шина позволяет уменьшить мощность (ток), потребляемую устройствами, ценой снижения производительности, применяя пошаговое переключение линий AD[31:0] и PAR (address/data stepping). Здесь возможны два варианта.

♦ Плавный | шаг (continuous | stepping) — | начало | формирования | сигналов слабо |

точными | формирователями | за несколько | тактов | до введения | сигнала-квалифи- |

катора действительной информации (FRAME# в фазе адреса, IRDY# или TRDY# вфазеданных). Заэтинесколькотактовсигналы«доползут» дотребуемогозначения применьшем токе.

♦Дискретный шаг (diskrete stepping) — нормальные формирователи срабатывают не все сразу, а группами (например, побайтно), в каждом такте по группе. При этом снижаются броски тока, поскольку одновременно переключается меньше формирователей.

studfiles.net

21.1.3.2. Локальная шина pci

В начале 1992 года на фирме Intel была организована группа, перед которой была поставлена задача разработать новую шину. В результате в июне 1992 года появилась шина PCI (Peripheral Component Interconnect bus), в апреле 1993 она была модернизирована. Ее создатели отказались от традиционной концепции, введя еще одну шину между МП и обычной шиной ВВ. Вместо того чтобы подключаться непосредственно к шине процессора, чувствительной к подобным вмешательствам (о чем сказано выше), новый комплект ИС (чипсет) позволял создавать новую архитектуру шин IBM PC. Первые компьютеры с шиной PCI появились в середине 1993 года, и вскоре она стала неотъемлемой частью компьютеров класса high end.

Новая локальная шина существенно превосходила своих предшественниц по функциональным возможностям, производительности, надежности. Наличие чипсета делает шину PCI процессорно-независимой, что позволяет ее использовать с платформами не только на Intel-подобных процессорах. Это является очевидным преимуществом с точки зрения производителей плат расширения (адаптеров), которые стараются избегать разных версий одной и той же платы. Кроме того, наличие чипсета позволяет шине PCI работать параллельно с шиной процессора, не обращаясь к ней со своими запросами. Это даёт возможность процессору работать с данными, находящимися во внешнем кэш, в то время как по шине PCI может происходить обмен между ПУ и ОП в режиме ПДП (DMA).

Первоначально в IBM PC использовалась только версия 2.0 шины PCI, поддерживаемая чипсетами малой интеграции (5-6 микросхем) типа Neptun или Saturn. Однако с появлением чипсетов большей интеграции типа Intel 430 (Triton), Intel 440, Intel 810 в IBM PC стала использоваться новая версия шины PCI-2.1, которая вскоре была заменена версией PCI-2.2 (например, чипсет Intel 815). Эта версия используется и в настоящее время (чипсеты Intel 850, Intel 860, VIA KT 266 для процессоров AMD и др.). Версии 2.0, 2.1 и 2.2 имеют обратную совместимость на тактовой частоте 33 МГц. Основные возможности шины PCI следующие:

Синхронный 32- или 64-разрядный обмен данными. Для уменьшения числа линий шины и контактов слота (а следовательно, и стоимости) используется мультиплексирование ША и ШД, т.е. для передачи адресов и данных используются одни и те же линии шины. Поддержка режима пакетных передач (linear burst), позволяющего не расходовать время шины на установку адреса каждого элемента данных при обмене блоком информации. Адрес автоматически модифицируется чипсетом для каждого последующего элемента данных. Это существенно повышает производительность шины при обмене ядра ЭВМ с видеосистемами и жесткими дисками большими блоками информации.

Тактовая частота шины 33 МГц или 66 МГц (только для версий выше 2.0). Это позволяет обеспечить следующие максимальные пропускные способности шины с использованием пакетного режима:

132 Мбайт/с при 32-бита/33 МГц;

264 Мбайт/с при 32-бита/66 МГц;

264 Мбайт/с при 64-бита/33 МГц;

528 Мбайт/с при 64-бита/66 МГц.

Работа на тактовой частоте 66 МГц возможна, если все адаптеры шины поддерживают эту частоту.

Поддержка внешнего кэш с обратной и сквозной записью (write back и write through).

Автоматическое конфигурирование карт расширения при включении питания.

Полная поддержка режима multiply bus master, при котором на шине одновременно могут работать, например, несколько контроллеров жестких дисков.

Установка запросов прерывания осуществляется по уровню (а не по фронту, как в шинах ISA и VLB), что делает систему прерывания более надежной и позволяет использовать одну линию прерывания для обслуживания нескольких ПУ.

Спецификация шины позволяет комбинировать до восьми функций на одной плате (например, видео + звук + и т.д.).

Шина позволяет устанавливать до четырех слотов расширения, конструкция которых существенно отличается от конструкции слотов шины ISA (EISA). Для увеличения числа подключаемых устройств (необходимость в этом возникает обычно в мощных серверных платформах) предусмотрено использование двух и более шин PCI, соединяемых одноранговыми мостами (peer-to-peer bridge). Следует отметить, что с разработкой нового поколения чипсетов (например, Intel 850, Intel 845, Intel 815, VIA KT 266 и др.) число слотов расширения, устанавливаемых на одной шине PCI, увеличилось до 5-6.

Шина PCI имеет версии с питанием 5 В и 3.3 В. Разъемы для плат с питанием 5 В и 3.3 В различаются расположением ключей. Существуют и универсальные платы с переключаемым напряжением питания. Тактовая частота 66 МГц поддерживается только логикой питания 3.3 В.

Наличие в устройстве шины PCI таймера, используемого для определения максимального интервала времени, в течение которого устройство может занимать шину при передаче блока информации.

Рассматривая возможности шины PCI, необходимо иметь в виду, что чипсет является не просто согласующим элементом между различными шинами PC. Он основное связующее звено между всеми компонентами системной платы. Набор решаемых им задач очень обширен и во многом определяет характеристики конкретной модели компьютера, поэтому рассмотрение функциональных возможностей PCI-архитектуры в отрыве от функций чипсета весьма затруднительно. Так, например, возможность выполнения обмена данными между процессором и ОП одновременно с обменом между другими устройствами шины PCI (concurrent PCI transferring), предусмотренная в спецификации шины, реализована не во всех типах чипсетов.

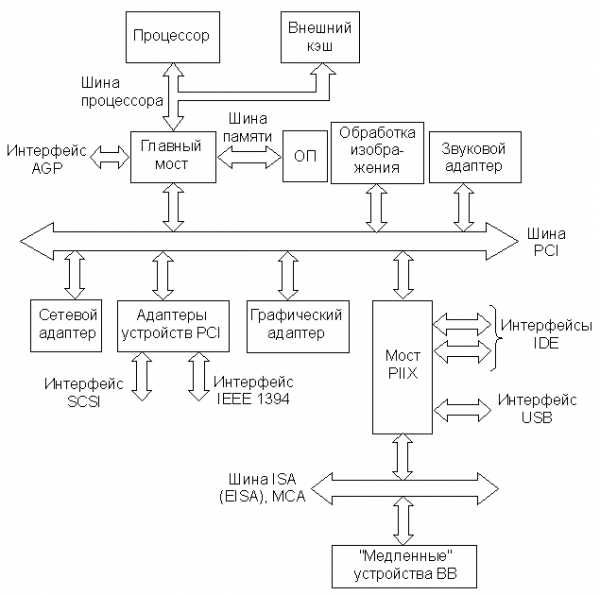

В общем случае чипсет можно разделить на две функциональные части. Одна часть чипсета обеспечивает взаимодействие шины PCI с локальной системной шиной (т.е. с шиной процессора и шиной памяти). Эту часть принято называть главным мостом (host bridge), северным мостом (northbridge) или контроллером-концентратором памяти (Memory Controller Hub, MCH). Вторая часть обеспечивает взаимодействие шины PCI с жёстким диском, картами PSI и низкоскоростными интерфейсами, типа ШР ISA, PCI Express, интерфейсами IDE, SATA, USB и т.п. Эту функциональную часть чипсета принято называть мостом PIIX (PCI, IDE, ISA Xcelerator bridge), южным мостом ( southbridge) или контроллером-концентратором ввода-вывода (I/O Controller Hub, ICH). Такому функциональному делению соответствует и разделение набора задач, решаемых чипсетом. Чаще всего чипсет современных материнских плат состоит из двух основных микросхем (MCH и ICH), но иногда их объёдиняют в одну микросхему (чип) и называют системным контроллером-концентратором (System Controller Hub, SCH).

В функции главного моста входит решение следующих задач:

Обслуживание управляющих и конфигурационных сигналов процессора.

Мультиплексирование адреса и формирование управляющих сигналов динамической памяти (ОП), связь шины данных памяти с локальной шиной.

Формирование управляющих сигналов внешнего кэш, сравнение его тегов с текущим адресом обращения на локальной шине (т.е. выполнение функций контроллера кэш-памяти).

Обеспечение когерентности (согласования) данных в обоих уровнях кэш-памяти и ОП при обращении как со стороны процессора, так и контроллеров устройств шины PCI.

Связь мультиплексированной шины адреса и данных шины PCI с шиной процессора и шиной ОП.

Формирование управляющих сигналов шины PCI, арбитраж контроллеров устройств шины (т.е. выполнение функций арбитра шины PCI).

Поддержка магистрального интерфейса AGP (Accelerated Graphic Port), предназначенного для подключения мощных графических адаптеров.

Мост PIIX также является многофункциональным устройством и решает следующие задачи:

Организацию моста между шинами PCI b жёстким диском, картами PSI и низкоскоростными интерфейсами, типа ШР ISA, PCI Express, интерфейсами IDE, SATA, USB и т.п. с согласованием частот синхронизации этих шин.

Реализацию стандартных системных средств ВВ – контроллеров прерываний, контроллеров ПДП, системного таймера, канала управления динамиком, логики немаскируемого прерывания и т.п.

Коммутацию линий запросов прерывания шин PCI и других шин, а также встроенной периферии на линии запросов контроллеров прерываний, управление их чувствительностью (по перепаду или уровню), обслуживание прерывания от сопроцессора.

Коммутацию каналов ПДП.

Поддержку режимов энергосбережения.

Реализацию моста с внутренней шиной X-Bus, используемой для подключения микросхем контроллера клавиатуры, BIOS, CMOS RTC, контроллеров гибких дисков и интерфейсных портов.

Микросхемы чипсета при инициализации во время начального тестирования (POST) программируются по многим параметрам, основная часть которых находится в BIOS. Таким образом, системные платы, выполненные даже на одном и том же чипсете, могут иметь различные производительности и диапазоны поддерживаемых устанавливаемых компонентов (процессоров, DRAM, кэш). Соответственно и шины PCI, реализованные в различных моделях РС (особенно у разных производителей), могут несколько отличаться по своим функциональным возможностям.

Очень упрощенная структура шин IBM РС (с учетом функций чипсета) при наличии шины PCI представлена на рис. 21.3.

Обозначенные на схеме интерфейсы для подключения высокоскоростных ПУ (AGP, SCSI, IEEE 1394, IDE, USB) в настоящем разделе не рассматриваются. Отметим только, что многие модели современных IBM PC имеют еще ряд других (не обозначены на схеме) специализированных интерфейсов для подключения разнообразных типов ПУ.

Для устройств промышленного назначения в начале 1995 года был принят стандарт Compact PCI, разработанный на основе версии PCI 2.1. Шины Compact PCI и PCI имеют электрическую совместимость и одинаковые протоколы обмена по шине, хотя и имеют некоторые отличия в механизме автоконфигурации системы. В отличие от стандарта PCI стандарт Compact PCI позволяет устанавливать на одной шине до восьми слотов расширения, конструкция которых существенно отличается от конструкции слотов PCI и предназначена для работы компьютера в тяжелых условиях – пыль, вибрация, влажность и т.д.

В заключение следует отметить, что появление шины PCI положило начало полному вытеснению из РС фирмы IBM, в общем-то, устаревшей ШР ISA. В настоящее время шина ISA оказалась практически вытесненной из архитектуры IBM PC и все ее функции выполняет шина PCI, которая из локальной превратилась в основную ШР современных IBM PC.

Рис.21.3. Упрощённая структура шин IBM PC

studfiles.net

Общая характеристика шины PCI

PCI (Peripheral Component Interconnect) local bus- шина соединения периферийных компонентов. Она разрабатывалась в расчете на шинный интерфейс процессоров Pentium. В архитектуре ЭВМ эта шина стала центральной, через которую процессор взаимодействует со всеми остальными шинами (см. рисунок 8.7). Первая версия стандарта шины PCI 1.0 появилась в 1992 г., PCI 2.1 - в 1995 г.

Шина PCI является синхронной шиной, в которой фиксация всех сигналов выполняется по нарастающему фронту сигнала синхронизации CLK (см. рисунок 8.4.3). Номинальное значение частоты синхронизации CLK равно 33 МГц. Начиная с версии 2.1 допускается повышение частоты CLK до 66 МГц.

Шина PCI относится к мультиплексированным шинам, в которой для передачи адреса и данных (последовательно во времени) используются одни и те же линии. Номинальная разрядность ШД и ША- 32бита, возможно увеличение их разрядности до 64 бит. При частоте шины 33 МГц пропускная способность шины равна 132 Мбайт/с для 32 разрядной шины и 264 Мбайт/с для 64- битной шины.

Подключенные к шине устройства (функции) представляются процессору непосредственно подключенными к его шине. Им назначаются адреса из адресного пространства памяти или УВВ. Дешифрирование адреса на шине PCI распределено, т.е. выполняется в каждом устройстве. Каждое устройство отвечает только на свой адрес. Спецификация PCI требует перемещаемости всех занимаемых ресурсов в пределах доступного пространства адресации, что обеспечивает их бесконфликтное распределение для многих устройств.

С устройствами PCI процессор может взаимодействовать командами обращения к памяти и портам ввода-вывода, адресованным к областям, выделенным данному устройству при конфигурировании системы. Устройства могут вырабатывать запросы маскируемых и немаскируемых прерываний. Понятие каналов ПДП для шины PCI не вводится, но устройство может выступать в роли задатчика, поддерживая высокопроизводительный обмен с памятью без привлечения процессора. Так может быть реализован обмен в режиме ПДП с устройствами IDE, подключенными к мосту PCI- ISA (см. рисунок 8.5).

Основные сигналы шины

CLK - сигнал синхронизации работы устройств. Является входным сигналом для каждого PCI - устройства. Все сигналы PCI, за исключением RST#, IRQA#, IRQB#, IRQC# и IRQD# фиксируются по нарастающему фронту сигнала CLK.

RST# - сигнал сброса устройств в исходное состояние.

AD[31::00]- сигналы адреса данных. Адрес и данные последовательно во времени выдаются (мультиплексированы) на одни и те же линии шины PCI. Транзакция (обмен) шины состоит из фазы адреса, сопровождаемой одним или большим количеством фаз данных. В течение фазы адреса на линии AD[31::00] выдается физический адрес (32 бита) устройства. В фазе данных на лини AD[31::00] выдаются данные, при этом разряды AD[07::00] содержат младший значащий байт, а AD[31::24] содержат старший значащий байт.

C/BE[3::0]# (Bus Command и Byte Enables)- команды шины и разрешение байта. Сигналы мультиплексированы на одних и тех же линиях шины. Во время фазы адреса транзакции, сигналы C/BE[3::0]# определяет команду шины (смотри раздел 3.1). В течение фазы данных сигналы C/BE[3::0]# используется в качестве сигналов Byte Enable т.е определяют, какие байты действительны, а какие не используются.

FRAME# (Кадр). Активный уровень сигнала означает начало транзакции (с фазы адреса). Снятие сигнала указывает, что последующий цикл передачи данных является последним в транзакции.

IRDY# (Initiator Ready)- готовность инициатора к обмену. Сигнал показывает, что на линиях AD[31::00] присутствуют достоверные данные. При чтении данных сигнал означает готовность мастера к приему данных.

TRDY#( Target Ready )- целевое устройство готово. Показывает способность целевого агента (выбранного устройства) завершить текущую фазу данных транзакции. Используется совместно с сигналом IRDY#. При чтении TRDY# указывает, что на линиях AD[31::00] присутствуют достоверные данные. Во время записи это означает готовность целевого устройства к принятию данных. Циклы ожидания вставляются до тех пор, пока активны оба IRDY# и TRDY#.

DEVSEL# (Device Select )- устройство выбрано. Сигнал показывает, что ЦУ дешифрировало адрес, выданный на шину AD. Используется в качестве ответа ЦУ инициатору обмену на адресованную к нему транзакцию.

INTA#, INTB#, INTC# и INTВ# (Interrupt A…D) – входы запросов прерываний. Активным уровнем сигнала прерывания является лог. 0, при этом для устройств используется выход с открытым коллектором. Переход сигналов INTx# в активное состояние и обратно асинхронно по отношению к сигналу CLK.

REQ# (Request) – запрос. Сигнал показывает арбитру, что данному агенту требуется поработать с шиной. Каждый мастер имеет свой индивидуальный вывод REQ#.

GNT# (Grant)- разрешение. Сигнал показывает агенту, что разрешен доступ к шине. Каждый мастер имеет свой индивидуальный вывод GNT#.

Протокол шины PCI

В каждой транзакции (обмене по шине) участвуют два устройства- инициатор (initiator) обмена, он же мастер (master) или ведущее устройство и целевое (target) устройство (ЦУ), оно же ведомое (slave). Шина PCI все транзакции трактует как пакетные. Каждая транзакция начинается фазой адреса, за которой могут следовать одна или несколько фаз данных (см. рисунок 8.7).

В каждый момент времени шиной может управлять только один мастер, получивший на это право от арбитра шины. Каждый мастер имеет пару сигналов- REQ# для запроса управления шиной и GNT# для подтверждения предоставления управления шиной. Устройство может начинать транзакцию (устанавливать сигнал FRAME# ) только при активном полученном сигнале GNT#. Арбитраж запроса на использование шины выполняет арбитр шины, входящий в состав контроллера шины PCI, в свою очередь входящего в состав чипсета северного моста системной платы ЭВМ.

Для передачи адреса и данных используются общие мультиплексированные линии AD[31::00]. Четыре мультиплексированные линии C/BE[3::0]# обеспечивают кодирование команд в фазе адреса транзакции и разрешение байт в фазе данных. Для начала транзакции инициатор обмена должен активизировать сигнал FRAME# (т.е установить его в лог. 0), вслед за чем выставить на шину AD[31::00] адрес ЦУ, а на линии C/BE[3::0]# - информацию о типе транзакции (команду).

Рисунок 8.7 - Цикл обмена шины PCI

Адресованное ЦУ после дешифрации адреса должно заявить о своем присутствии сигналом DEVSEL#. Для продолжения обмена инициатор должен указать на свою готовность к обмену данными активизацией сигнала IRDY#. Когда к обмену данными будет готово и ЦУ оно должно активизировать сигнал TRDY#. Данные по шине AD могут передаваться только при активных уровнях обеих сигналов IRDY# и TRDY#. С помощью этих сигналов инициатор и ЦУ согласуют свои скорости обмена, вводя такты ожидания.

Транзакции заканчиваются переводом сигналов FRAME# и IRDY# в пассивное состояние (состояние лог.1).

8.5 Контрольные вопросы

1. Перечислите названия шин, входящих в состав системной платы ЭВМ IBM PC/AT 286.

2. Назовите разрядность ША и ШД периферийной шины и шины ISA.

3. Чем обусловлено использование в архитектуре ПК IBM PC/AT 286 четырех шин?

4. Каково назначение ШФ?

5. Какое основное отличие ШФ ША и ШД?

6. Количество кварцевых резонаторов в системной плате IBM PC/AT 286.

7. На каких микросхемах построена подсистема прерываний IBM PC/AT 286.

8. Каково назначение порта B в ЭВМ IBM PC/AT 286.

9. Каково назначение CMOS – памяти .

10. Перечислите названия шин, входящих в состав системной платы ЭВМ IBM PC/AT Pentium.

11. К какому типу шин относится шина PCI?

12. Каково назначение сигналов FRAME# и IRDY#?

13. Количество прерываний, используемых в ЭВМ IBM PC/AT 286?

14. Назначение прерываний IRQ0 и IRQ1?

15. Значения тактовых частот шины PCI?

Библиографический список

- Каган Б.М. Электронные вычислительные машины и системы: Учеб. пособие для вузов. – 2-е изд. перераб. и доп. – М.: Энергоатомиздат, 1985. – 552с., ил.

2. Организация ЭВМ. 5-е изд./К. Хамахер, З. Вранешич, С. Заки.- СПб.: Питер; Киев: Издательская группа BHV, 2003. – 848 с.: ил.

3. Цилькер Б. Я., Орлов С. А. Организация ЭВМ и систем: Учебник для вузов. – СПб.: Питер, 2004. – 668 с.: ил.

4. Гук М. Аппаратные средства IBM PC. Энциклопедия. 2-е изд. – СПб.: Питер. 2001. – 928 с.: ил.

5. Сергеев Н.П., Вашкевич Н.П. Основы вычислительной техники: Учеб. пособие для электротехн. специальн. вузов. – 2-е изд. перераб. и доп. – М.: Высш. шк., 1988. – 311с., ил.

6. Балашов Е.П. и др. Микро- и мини ЭВМ: Учеб. пособие для вузов. - Л.: Энергоатомиздат, Ленингр. отд-ние, 1984. – 376с., ил.

7. Балашов Е.П., Пузанков Д.В. Микропроцессоры и микропроцессорные системы: Учеб. пособие для вузов/Под ред. В.Б. Смолова.- М., ”Радио и связь”,1981. – 328с., ил.

8. Бикташев Р.А., Князьков В.С. Многопроцессорные системы. Архитектура, топология, анализ производительности: Учеб. пособие.- Пенза: Пенз. гос. ун-т, 2003. - 217 с.

9. Компьютеры на СБИС: В 2-х кн. Кн. 2: Пер. с япон./ Мотоока Т., Сакаути М., Харикоси Х. И др.- М.: Мир, 1988.- 336с.

10. Сетевые операционные системы/ В.Г. Олифер, Н.А. Олифер.- СПб.: Питер. 2001. –544 с.

11. Шагурин И.И., Бердышев Е.М. Процессоры семейства Intel P6. Архитектура, программирование, интерфейс.- М.: Горячая линия - Телеком, 2000.- 248 с.

12. Корнев В.В., Кисилев А.В. Современные микропроцессоры.- М.: Нолидж, 1988. - 240 с.

13. Карасев В. В., Кисилев А.В. Современные микропроцессоры- 3-е изд., перераб и доп. СПб.: БХВ- Петербург, 2003. -448 с.

14. Таненбаум Э. Архитектура компьютера. 4-е изд. СПб.: Питер, 2003.-704 с.

Содержание

1 ОБЩИЕ СВЕДЕНИЯ О ЭВМ…………………………...3

1.1 Этапы развития ЭВМ ………………………………….3

1.2 Характеристики ЭВМ…………………………………..6

1.3 Классификация средств ЭВТ………………………….10

1.4 Структуры ЭВМ………………………………………..12

1.4.1 Обобщенная структура ЭВМ……………………..…12

1.4.2 Структура ЭВМ на основе общей шины…………....13

1.4.3 Структура ЭВМ на основе множества шин………...14

1.5 Контрольные вопросы…………………………………17

2 АРХИТЕКТУРА КЛАССИЧЕСКОЙ ЭВМ…………….18

2.1 Принцип программного управления………………….18

2.2 Принцип хранимой в памяти программы…………….19

2.3 Обобщенный формат команд………………………….20

2.4 Способы адресации команд……………………………21

2.4.1 Процессоры с принудительным порядком выполнения команд………………………………………………………………22

2.4.2 Процессоры с естественной адресацией команд……24

2.5 Способы адресации операндов…………………………25

2.5.1 Прямая адресация……………………………………..25

2.5.2 Регистровая адресация ……………………………….27

2.5.3 Косвенная адресация …………………………………27

2.5.4 Непосредственная адресация…………………………28

2.5.5 Неявная адресация……………………………………29

2.5.6 Относительная (базовая) адресация………………….29

2.5.7 Индексная (автоинкрементная или автодекрементная) адресация…………………………………………………………...30

2.6 Контрольные вопросы………………………………….31

3. ЗАПОРМИНАЮЩИЕ УСТРОЙСТВА ЭВМ………….33

3.1 Основные понятия……………………………………...33

3.2 Классификация ЗУ……………………………………...34

3.3 ОЗУ с произвольным доступом………………………..37

3.4 Организация микросхем SRAM ……………………….40

3.5 Организация динамической памяти …………………...42

3.6 Особенности микросхем синхронной динамической памяти……………………………………………………………….45

3.7 Основные характеристики ЗУ…………………………..46

3.8 ОЗУ магазинного типа (стековая память)……………..48

3.9 Ассоциативные ЗУ………………………………………50

3.10 Контрольные вопросы…………………………………54

4. ПРИНЦИПЫ ОРГАНИЗАЦИИ ПРОЦЕССОРОВ……56

4.1 Обобщенные структуры процессоров с непосредственными и магистральными связям…………………56

4.2 Декомпозиция процессора на УА и ОУ……………….58

4.3 Арифметико-логические устройства…………………..59

4.3.1 Классификация арифметико-логических устройств..59

4.3.2 АЛУ для сложения и вычитания чисел с фиксированной запятой……………………………………………60

4.3.3 АЛУ для умножения двоичных чисел……………….64

4.3.4 Методы ускорения умнож.ения………………………70

4.3.5 Особенности операций десятичной арифметики…...72

4.3.6 Операции над числами с плавающей запятой………74

4.4 Устройства управления………………………………...76

4.4.1 Классификация УУ…………………………………...76

4.4.2 Аппаратные УУ………………………………………77

4.4.3 Микропрограммные УУ……………………………...79

4.5 Структурно - функциональная организация классического процессора………………………………………...83

4.6 Рабочий цикл процессора………………………………86

4.7 Понятие о слове состояния процессора (PSW)………87

4.8 Процедура выполнения команд перехода (условного и безусловного)………………………………………………………88

4.9 Процедура выполнения команд вызова подпрограмм..………………………………………………….…..89

4.10 Контрольные вопросы………………………………...91

5. СИСТЕМЫ ПРЕРЫВАНИЯ ПРОГРАММ……………..92

5.1 Общие сведения………………………………………...92

5.2 Характеристики систем прерываний…………………..95

5.3 Схема выполнения процедуры прерывания…………...96

5.4 Способы реализации систем прерываний……………..97

5.4.1 Схема прерывания с опросом по вектору…………...97

5.4.2 Прерывания с программно - управляемым приоритетом………………………………………………………..98

5.5 Контрольные вопросы…………………………………..99

6. ОРГАНИЗАЦИЯ ВВОДА – ВЫВОДА………………...100

6.1 Общие сведения о вводе-выводе в ЭВМ……………..100

6.2 Основные способы ввода-вывода…………………….100

6.2.1 Программно - управляемый ввод – вывод…………101

6.2.2 Ввод - вывод с прерыванием программы…………..103

6.2.3 Ввод – вывод в режиме ПДП………………………..103

6.3 Интерфейсы…………………………………………….104

6.3.1 Характеристики интерфейсов……………………….105

6.3.2 Шины интерфейсов ввода-вывода…………………105

6.3.2.1 Синхронные шины…………………………………106

6.3.2.2 Асинхронные шины………………………………..108

6.4 Контрольные вопросы…………………………………109

7. ОРГАНИЗАЦИЯ ПАМЯТИ ЭВМ С МАГИСТРАЛЬНОЙ СТРУКТУРОЙ…………………………………………………….110

7.1 Организация адресного пространства памяти и ввода-вывода. Изолированная и совмещенная адресные пространства………………………………………………………110

7.1.1 Изолированное адресное пространство памяти и ввода- вывода……………………………………………………...110

7.1.2. Совмещенное адресное пространство памяти и ввода- вывода……………………………………………………………...112

7.2 Организация ПЗУ. Проектирование памяти ЭВМ…...113

7.3 Построение оперативной памяти на микросхемах статического типа…………………………………………………116

7.4 Построение оперативной памяти на микросхемах DRAM……………………………………………………………...118

7.5 Память с чередованием адресов………………………119

7.6 Регенерация динамической памяти…………………..121

7.7 КЭШ-память…………………………………………...122

7.7.1 КЭШ прямого отображения ………………………...124

7.7.2 Наборно - ассоциативный КЭШ…………………….127

7.8 Контрольные вопросы………………………………...128

8 ОРГАНИЗАЦИЯ ПК…………………………………….129

8.1 Структурная схема системной платы ЭВМ IBM PC/AT 286………………………………………………………………….129

8.1.1 Система шин системной платы ЭВМ IBM PC/AT 286 ……………………………………………………………………...129

8.1.2 Состав и назначение основных устройств системной платы ЭВМ IBM PC/AT 286……………………………………...131

8.1.2.1 Назначение и характеристики процессора и сопроцессора………………………………………………………131

8.1.2.2 Назначение и характеристики генераторов тактовых сигналов……………………………………………………………132

8.1.2.3 Назначение шинных формирователей…………...132

8.1.2.4 Формирование управляющих сигналов и работа подсистемы памяти……………………………………………….133

8.1.2.5 Назначение и характеристики периферийных устройств системной платы……………………………………...133

8.1.2.6 Назначение ПЗУ BIOS……………………………..137

8.1.3 Шина ISA……………………………………………..137

8.1.3.1 Особенности шины ISA……………………………137

8.1.3.2 Основные сигналы шины ISA……………………..138

8.1.3.3 Шинные циклы магистрали ISA…………………..142

8.1.3.4 Электрические и конструктивные характеристики шины ISA………………………………………………………….145

8.1.3.5 Конвейеризация шины…………………………….146

8.2 Структурная схема системной платы ЭВМ IBM PC/AT Pentium………………………………………….............................147

8.2.1 Локальные шины ввода – вывода………………….147

8.2.2 Состав и назначение основных устройств системной платы ЭВМ IBM PC/AT Pentium………………………………..148

8.3 Основные сигналы шинного интерфейса процессора Pentium…………………………………………………………….149

8.4 Организация шины PCI………………………………..152

8.4.1 Общая характеристика шины PCI…………………..152

8.4.2 Основные сигналы шины……………………………153

8.4.3 Протокол шины PCI………………………………….155

8.5 Контрольные вопросы…………………………………156

Библиографический список…………………………...158

infopedia.su

FSB, шины расширения, внешние компьютерные шины.

Шины